Synopsys, Inc. announced the availability of the new DesignWare ARC HS4x and HS4xD

“Our design team is under constant pressure to achieve higher performance for our SSD controllers to keep up with the rapidly evolving enterprise market,” said Sky Shen, CEO at Starblaze. “Synopsys’ new ARC HS4x and HS4xD processors will enable us to achieve new levels of performance while limiting power consumption and chip area, which is very important in our application. Additionally, the ARC development tools and ecosystem will help us accelerate our software development effort and project schedules.”

“Our design team is under constant pressure to achieve higher performance for our SSD controllers to keep up with the rapidly evolving enterprise market,” said Sky Shen, CEO at Starblaze. “Synopsys’ new ARC HS4x and HS4xD processors will enable us to achieve new levels of performance while limiting power consumption and chip area, which is very important in our application. Additionally, the ARC development tools and ecosystem will help us accelerate our software development effort and project schedules.”

“A growing number of embedded applications require a combination of high-performance RISC execution and energy-efficient signal processing,” said Linley Gwennap, principal analyst at The Linley Group. “Synopsys’ new HS4xD processors, with their superscalar architecture and hardware DSP support, give SoC designers an alternative to implementing separate CPU and DSP cores, saving power and silicon gates.”

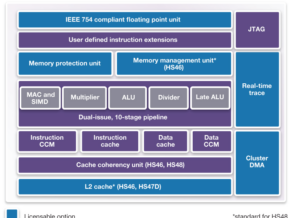

The ARC HS44, HS46 and HS48 processors utilize the ARCv2 instruction-set architecture (ISA), which enables the implementation of high-performance embedded designs with low power consumption and a small silicon footprint. The ARC HS4x family features a high-speed 10-stage, dual-issue pipeline that supports out-of-order execution, minimizing idle processor cycles and maximizing instruction throughput. The processors deliver up to 6000 DMIPS per core at 2.5 GHz while requiring only 0.06 mm2 of area and as little as 37 microwatts/MHz in typical 16-nm FinFET processes. The sophisticated branch prediction and a late-stage ALU reduce load-to-use latency to improve instruction processing efficiency. The HS4x processors are available in single-, dual- and quad-core configurations that deliver up to 24,000 DMIPS per cluster. The HS46 and HS48 offer instruction and data caches (up to 64 KBs of each) and support for full Level 1 (L1) cache coherency. The HS48 also incorporates up to eight megabytes of Level 2 (L2) cache as well as a full-featured memory management unit (MMU) supporting symmetric multiprocessing (SMP) Linux. Like all ARC processors, all HS4x processors are configurable and implement the ARC Processor EXtension (APEX) technology that enables the addition of custom instructions to meet the unique performance, power and area requirements of each target application.

The HS45D and HS47D offer the same high-end control features of their HS4x counterparts with additional DSP capabilities useful for baseband, audio, voice, speech and other signal processing applications. To speed the execution of math functions, the HS45D and HS47D give designers the option to implement a hardware integer divider, instructions for 64-bit multiply, multiply-accumulate (MAC), vector addition and vector subtraction, and a configurable IEEE 754-compliant floating point unit (single- or double-precision or both). The ARC HS4xD processors are compatible with the ultra-low power ARC EMxD processors and have the same instruction set, making it easy to migrate code between the two processor families.

The blend of high-performance RISC and DSP capabilities in the HS4xD processors provides efficient multi-channel audio processing for mobile, home and automotive infotainment applications. The HS4xD can simultaneously manage control tasks such as communications stacks and filesystem support while providing the signal processing bandwidth to support audio decoding, post-processing and voice-based HMI processing. These tasks are critical to high-performance wireless streaming speaker systems and voice-activated assistants found in an increasing number of homes. A portfolio of HS4xD-optimized audio/voice codecs and post-processing software is available from Synopsys and third-party partners.

The ARC HS44, HS46, HS48, HS45D and HS47D processors are scheduled to be available in June 2017.

Leave a Reply