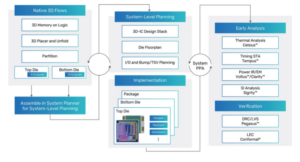

The comprehensive, high-capacity 3D-IC platform from Cadence Design System integrates 3D design planning, implementation, and system analysis in a single, unified cockpit. The Integrity 3D-IC platform underpins Cadence’s third-generation 3D-IC solution, providing customers with system-driven power, performance, and area (PPA) for individual chiplets through integrated thermal, power, and static timing analysis capabilities. Chip designers creating […]

cadencedesignsystems

Logic simulator adds machine learning to speed verification tasks

Cadence Design Systems, Inc. announced that the Cadence Xcelium Logic Simulator has been enhanced with machine learning technology (ML), called Xcelium ML, to increase verification throughput. Using new machine learning technology and core computational software, Xcelium ML enables up to 5X faster verification closure on randomized regressions. Using computational software and a proprietary machine learning […]

Automated security validation platform identifies vulnerabilities in firmware and SoC designs

Tortuga Logic, a cybersecurity company specializing in hardware threat detection and prevention, announced the launch of Radix-M, the industry’s first platform capable of performing security validation of firmware on complex system-on-chip (SoCs) designs. Built with funding support from the Defense Advanced Research Projects Agency (DARPA), Radix-M identifies and prevents unknown firmware vulnerabilities. It also automates previously manual […]

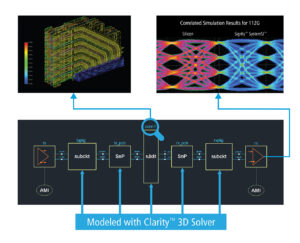

System design and analysis tackles electromagnetic challenges

Cadence Design Systems, Inc. entered the fast-growing system analysis and design market with the announcement of the Cadence Clarity 3D Solver, which delivers high accuracy with up to 10X faster simulation performance and unbounded capacity compared to legacy field solver technology. Harnessing state-of-the-art distributed multiprocessing technology, the Clarity 3D Solver efficiently tackles electromagnetic (EM) challenges […]

Chip design tools optimized for Arm Neoverse N1 platform in cloud-to-edge apps

Cadence Design Systems, Inc. announced that its tools and IP have been optimized to support the new Arm Neoverse N1 platform to accelerate the transformation of a scalable cloud-to-edge infrastructure. To ease adoption, Cadence delivered a 7nm full-flow digital implementation and signoff Rapid Adoption Kit (RAK), collaborated with Arm to ensure the Cadence Verification Suite […]

Cache coherent interconnect for accelerators test chip will use 7-nm FinFET process technology

Xilinx, Arm, Cadence Design Systems, Inc., and TSMC announced a collaboration to build the first Cache Coherent Interconnect for Accelerators (CCIX) test chip in TSMC 7nm FinFET process technology for delivery in 2018. The test chip aims to provide a silicon proof point to demonstrate the capabilities of CCIX in enabling multi-core high-performance Arm® CPUs […]

Chip IP helps implement advanced infotainment, ADAS SoCs in 16-nm FinFET Compact technology

Cadence Design Systems, Inc. today announced it is delivering a comprehensive automotive IP portfolio for the TSMC 16nm FinFET Compact (16FFC) automotive process technology. This broad IP portfolio enables a host of applications ranging from in-vehicle infotainment, in-cabin electronics, vision subsystems, digital noise reduction and advanced driver assistance system (ADAS) subsystems and is registered in […]