Aldec, Inc. has added an automatic UVM Generator function to Riviera-PRO. The addition promises to greatly boost the productivity of Riviera-PRO users taking advantage of the benefits of the Universal Verification Methodology, which contains guidance on the creation and reuse of verification test benches.

Aldec, Inc. has added an automatic UVM Generator function to Riviera-PRO. The addition promises to greatly boost the productivity of Riviera-PRO users taking advantage of the benefits of the Universal Verification Methodology, which contains guidance on the creation and reuse of verification test benches.

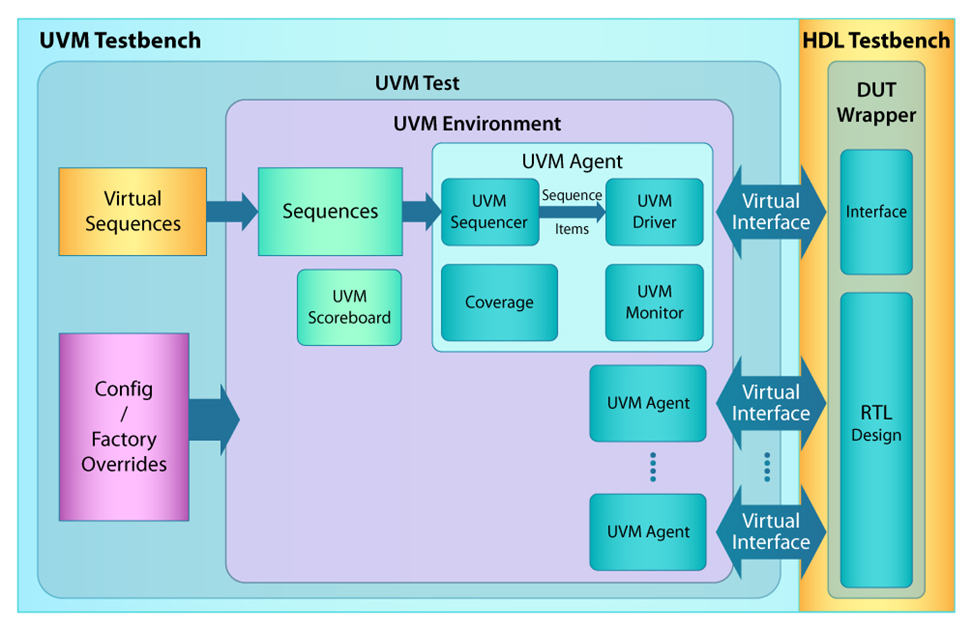

Riviera-PRO’s new function automatically creates the UVM testbench (in SystemVerilog, the language that underpins the methodology) for any given design under test (DUT) written in VHDL or Verilog. It also creates a framework of the UVM code; one that contains comments indicating places that must be manually populated with design-specific code. Along with SystemVerilog source files, the UVM Generator automatically creates the TCL macros for controlling the simulation process. The user can choose a DUT from a library or start a new design from scratch.

The UVM-generated code can also be displayed in Riviera-PRO’s UVM Graph Window, an existing and popular feature with users, for better visualization of the hierarchical UVM components, properties, connections, and dataflow – all of which greatly aid debugging.

Aldec has also updated the Open-Source VHDL Verification Methodology (OSVVM, a methodology the company played a significant role in creating) library to version 2021.06 within Riviera-PRO. In addition, the tool’s Universal VHDL Verification Methodology (UVVM) utility (uvvm_util) and VHDL Verification Component Framework (uvvm_vvc_framework) libraries have been updated to version v2021.05.26.

Riviera-PRO 2021.10 is now available for download and evaluation.

Leave a Reply