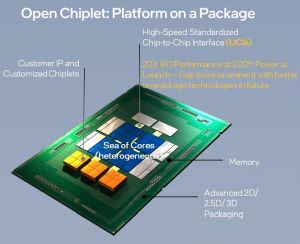

Support for the new UCIe (Universal Chiplet Interconnect Express) standard provides an efficient approach to enable design and verification engineers to leverage the recently-introduced standard for die-to-die interface connectivity. Avery’s offering includes high-quality models and test suites that support pre-silicon verification of systems using UCIe.

As part of the support for the standard, Avery Design Systems has joined the UCIe consortium which administers the specification, and includes founding members: Intel, AMD, Arm, Qualcomm,  TSMC, Samsung, ASE, Google, Microsoft and Meta.

TSMC, Samsung, ASE, Google, Microsoft and Meta.

UCIe was announced earlier this year as a mean to provide interoperability of chiplets within a package, enabling an open chiplet ecosystem and ubiquitous interconnect at the package level. The focus of the initial specification (Version 1.0) covers the UCIe Adapter and PHY including die-to-die I/O physical layer, Die-to-Die protocols, and software stack which leverage the well-established PCI Express (PCIe) and Compute Express Link (CXL) industry standards in addition to a protocol-agnostic raw transfer mode.

“As the use of various packaging methods evolves and grows, we are excited to be involved at the ground floor of this important new standard for enabling a more open, interoperable ecosystem for chiplet design. Much the way Avery has helped provide comprehensive verification IP solutions for SoC and IP companies, we believe giving engineers early access to reliable verification models and testsuites will help accelerate its use and be an important factor in realizing the vision of PCIe and CXL based chiplets based on UCIe and supporting its evolution,” said Luis E. Rodriguez, verification solutions architect at Avery.

“A key to success for any standard is a broad and robust ecosystem. Avery’s experience in enabling the adoption of open standards like CXL and PCIe demonstrates commitment to delivering timely, accurate design and verification tools to help meet the market requirements. We look forward to their participation in the adoption of UCIe to make chiplet interoperability a reality,” said UCIe Chairman and Intel Senior Fellow Dr. Debendra Das Sharma.

Avery offers a complete functional verification platform based on its robustly tested verification IP (VIP) portfolio that enables pre-silicon validation of design elements. Its UCIe offering supports standalone UCIe die to die adapter and LogPHY verification along with integrated PCIe and CXL VIP to run over the UCIe stack. In addition to UCIe models it provides comprehensive protocol checkers, coverage, reference testbenches, and compliance test-suites utilizing a flexible and open architecture.

Avery Design Systems, 1565 Main St STE 207, Tewksbury, MA 01876, (978) 851-3627, www.avery-design.com/