Anyone who has turned on a computer might be familiar with the boot-up sequence as computer flashes lines of text on screen before the Windows logo appears. What you are seeing is a bootloader in action, loading essential software to get the minimum running on the processor chip before higher-level software can run. Embedded bootloaders […]

Embedded

FACE-aligned RTOS runs on VPX SBCs

Continuing to build its safety certifiable portfolio and capability, Abaco Systems today announced availability of the LynxOS-178 2.2.4 real time operating system from Lynx Software Technologies (formerly LynuxWorks™) for Abaco’s DO-254 certifiable SBC 314 3U VPX single board computer (SBC). Because both the SBC314 and LynxOS-178 are true COTS (commercial off-the-shelf) products, customers can take […]

Top microcontroller threads on EDAboard.com – June

(editor’s note: Intrigued by the problem? Have a similar challenge? Have a question or another solution? Then click the “Read more” link and follow the conversation on EDAboard.com or log in to EDAboard and participate in the microcontroller forum thread.) Stuck in ISR, RCIF is not firing when UART with PIC18f5420 and SIM800 – I am […]

Board Support Package: what is it?

When designing a new system, you might find yourself drawn to a new processor with features that can make a real difference in the final product. Most semiconductor vendors will provide an evaluation board that you can use to evaluate whether or not you want to invest your time and money into that particular processor […]

Eclipse integrated development environment targets RISC-V open instruction set designs

Microsemi Corporation announced the release of its SoftConsole version 5.1, the world’s first available Windows-hosted Eclipse integrated development environment (IDE) for designs utilizing RISC-V open instruction set architectures (ISAs) such as RV32I. SoftConsole, Microsemi’s free software development environment enabling rapid production of C and C++ programming language designs for its field programmable gate arrays (FPGAs), will be showcased at […]

Image gallery: Cool autonomous vehicle tech at TU-Automotive Detroit

The recently wrapped-up TU-Automotive Detroit conference on autonomous and connected vehicles played host to 150 conference speakers and 3,000 people kicking tires in the 200,000-ft2 exhibition area. In the pages that follow are some of the more interesting technologies we found on display as we roamed the exhibit aisles. Taking a ride in a robotic […]

RTL-quality verification brought to the C-language level

Mentor, a Siemens business, today announced three new tools – Catapult Coverage, Catapult Design Checks and SLEC HLS – and enhancements to Catapult HLS. These new tools and enhancements further strengthen Mentor’s High-Level Synthesis (HLS) tool portfolio, which enables logic chip designers to cut project schedules by over 50 percent for applications such as machine vision, machine […]

Connected car platform incorporates RTOS, 64-bit security

Green Hills Software unveiled its Platform for Secure Connected Car, featuring the industry’s most comprehensive solution for vehicle and smart city manufacturers building vehicle-to-anything (V2X) and European car-to-anything (C2X) On-Board Units (OBU) and intelligent transportation infrastructure. Together with INTEGRITY Security Services (ISS), a Green Hills Software company, and first partners Autotalks and Commsignia, this Platform […]

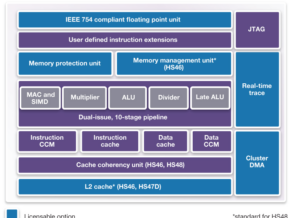

High-performance RISC processors add 2x DSP performance

Synopsys, Inc. announced the availability of the new DesignWare ARC HS4x and HS4xD processor family for high-performance embedded applications. The ARC HS44, HS46, HS48, HS45D and HS47D processors, available in single-, dual- and quad-core configurations, implement a dual-issue superscalar architecture that delivers up to 6000 DMIPS per core, making it the highest performance processor in the popular ARC HS […]

RISC architecture and instruction architecture

RISC stands for Reduced Instruction Set Computer and is a type of architectural processor design strategy. “Architecture” refers to the way a processor is planned and built and can refer to either the hardware or the software that is closest to the silicon on which it runs. An Instruction Set Architecture (ISA) specifies the basic […]