RISC-V International, a global open hardware standards organization, today announced the launch of the Open Hardware Diversity Alliance. The global Alliance, created by CHIPS Alliance, OpenPOWER Foundation,RISC-V, and Western Digital, will develop and provide learning and networking programs, mentorship opportunities and inclusive environments across the expansive ecosystem of open hardware. The Alliance will be focused […]

RISC-V

Updated reference model now includes RISC-V P extension and test suites

Imperas Software Ltd. announces the latest updates to riscvOVPsimPlus with support for the near ratified P extension and architectural validation test suites. The P (or Packed SIMD/DSP) extension is a significant addition to the flexibility of the modular RISC-V ISA (Instruction Set Architecture); it supports real-time data processing applications as part of the main processor pipeline […]

SDK supports latest Andes RISC-V extension and devices

IAR Systems presented a new version of its professional development tools for RISC-V. With the latest release, the complete development toolchain IAR Embedded Workbench for RISC-V adds support for the latest Andes RISC-V extension and devices, enabling maximized performance in RISC-V-based applications. Through its excellent optimization technology, IAR Embedded Workbench for RISC-V helps developers ensure […]

How does RISC-V fit into automotive systems?

RISC-V is being used in a surprising range of automotive systems ranging from ASIL-D safety rated controllers and security co-processors, artificial intelligence (AI) accelerators, controllers for advanced electric vehicle (EV) battery chargers based on gallium-nitride (GaN) power semiconductors, and even in high-voltage monolithic motor drive controllers for light EVs. The following is a sampling of […]

What’s the future for RISC-V in 5G?

The versatility of the RISC-V instruction set architecture (ISA) can be seen in the breadth of 5G applications using the technology. Examples include a complete 5G base station system-on-chip (SoC), a 5G small cell distributed unit (DU) SoC, a recurrent neural network (RNN) IC optimized for 5G radio resource management, even handsets are under development […]

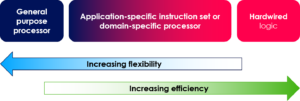

Domain specific accelerators for RISC-V

Domain specific accelerators (DSAs) are specialized hardware computing engines optimized for specific tasks. DSAs have been developed for graphics, simulation, image processing, deep learning, bioinformatics, and other tasks. Compared to general purpose processors, accelerators offer orders of magnitude improvements in performance/cost and/or performance/watt. The previous FAQ in this series, “What’s the future for RISC-V in […]

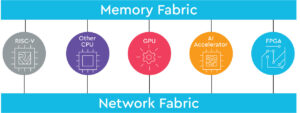

Memory, disk drives, memory fabrics and RISC-V

The unique and flexible computational architecture of RISC-V can be leveraged by designers of massive parallel computational storage solutions, hard disc drives (HDDs) and solid-state disk drives (SSDs), and memory fabric architectures such as Ethernet Bunch of Flash (EBOF) or Just a Bunch of Flash (JBOF) to implement high-performance solutions. This article will look at […]

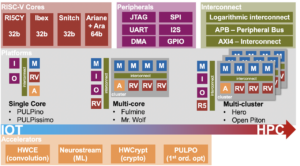

What is the RISC-V ecosystem?

In its most basic form, RISC-V is an open standard instruction set architecture (ISA) based on reduced instruction set computer (RISC) design principles. RISC-V is an open specification and platform; it is not an open-source processor. All other aspects of the RISC-V ecosystem build on that foundation. The hardware and software in the RISC-V ecosystem […]

RISC-V vs. ARM vs. x86 – What’s the difference?

Many of the differences between RISC-V, ARM, and x86 microprocessors are subtle and relate to how memory is addressed, branches are executed, exceptions are handled, and so on. This article will consider higher-level differences and will briefly compare reduced instruction set computing (RISC) and complex instruction set computing (CISC), consider the impact those differences have […]

RISC-V development tools certified for functional safety use

IAR Systems announces the availability of a certified edition of its development toolchain for RISC-V. The functional safety edition of IAR Embedded Workbench for RISC-V is certified by TÜV SÜD according to the requirements of IEC 61508, the international umbrella standard for functional safety, as well as ISO 26262, which is used for automotive safety-related […]