IAR Systems and Andes, the prominent CPU IP provider, announced that they have formed a partnership in order to deliver powerful development tools for Andes’ RISC-V-based solutions. IAR Systems provides the C/C++ compiler and debugger toolchain IAR Embedded Workbench. The toolchain offers leading code performance for size and speed, as well as extensive debug functionality […]

RISC-V

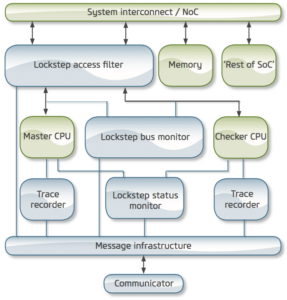

Lockstep monitor supports any processor architecture or subsystem

UltraSoC has launched the UltraSoC Lockstep Monitor, a hardware-based, scalable solution that helps functional safety significantly by checking that the cores at the heart of a critical system are operating reliably, safely and securely. UltraSoC’s flexible IP supports all common lockstep / redundancy architectures, including full dual-redundant lockstep, split/lock, master/checker, and voting with any number […]

Linux Foundation and RISC-V Foundation partner to accelerate RISC-V ISA

The Linux Foundation, the nonprofit organization enabling mass innovation through open source, and the RISC-V Foundation, a non-profit corporation controlled by its members to drive the adoption and implementation of the free and open RISC-V instruction set architecture (ISA), announced a joint collaboration agreement to accelerate open source development and adoption of the RISC-V ISA. The […]

High-performance RISC-V cores target 5G, networking apps

SiFive announced the availability of the SiFive Core IP 7 Series, the highest performance commercially available RISC-V cores. The 7 Series product family is designed to enable embedded intelligence with features that have not been commercially available until today. The 7 Series includes the E7, S7 and the U7 series. SiFive Core IP provides a truly […]

Expansion board broadens capabilities of RISC-V development board

Microsemi Corporation announced the launch of the HiFive Unleashed Expansion Board, its latest collaboration with SiFive, the first fabless provider of customized, open-source-enabled semiconductors. Leveraging the two companies’ strategic relationship as part of Microsemi’s Mi-V RISC-V ecosystem, the new expansion board broadens the capabilities of SiFive’s HiFive Unleashed RISC-V development board, further enabling software and […]

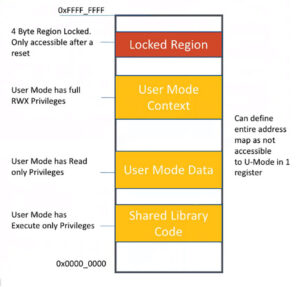

RISC-V: an Open Instruction Set Architecture

The benefits of open source have been bestowed upon an Instruction Set Architecture (ISA) called RISC-V. One of the earliest, best-known examples of open source technology is Linux. For a widely accepted, official definition of open source, see The Open Source Initiative. Open source does not stop at Linux, however. One of the more recent […]

FPGA development board for PolarFire designs

Microsemi Corporation and Future Electronics announced the availability of the Avalanche board featuring a Microsemi PolarFire non-volatile field programmable gate array (FPGA). As the lowest cost entry development board available today for designing with Microsemi’s lowest power, cost-optimized mid-range PolarFire FPGAs, Future’s Avalanche board lowers the barrier to entry for PolarFire FPGAs and helps expand Microsemi’s market opportunities for the device. The […]

RISC vs. CISC Architectures: Which one is better?

Reduced Instruction Set Computer (RISC) is a type or category of the processor, or Instruction Set Architecture (ISA). Speaking broadly, an ISA is a medium whereby a processor communicates with the human programmer (although there are several other formally identified layers in between the processor and the programmer). An instruction is a command given to […]

Top microcontroller stories of 2017

Here are the microcontroller features that got the most interest from readers in 2017. What is an open drain? Open-collector and -drain devices sink current when controlled to one state and have no current flow (i.e., output a high impedance state) in the other state. It is fairly common to use open-drains (open-collectors) together […]

RISC-V ecosystem surpasses 100 members globally

The RISC-V Foundation, a non-profit corporation controlled by its members to drive the adoption and implementation of the open, free RISC-V instruction set architecture (ISA) forward, today announced that the Foundation’s membership has exceeded more than 100 organizations, individuals, academics and universities from 19 countries and six continents around the world. Since its inception in 2015, […]