As discussed at the end of the first FAQ in this series, “RISC-V is growing and offers stability, scalability, and security,” there is a lack of testing standards and tools for RISC-V compared with mature ISAs such as Intel and Arm. This is an area that is experiencing accelerating developments and progress. The growing availability of tools that reduce the risk of using RISC-V is the focus of this FAQ. The following is a brief survey of some of the available tools; it is far from exhaustive.

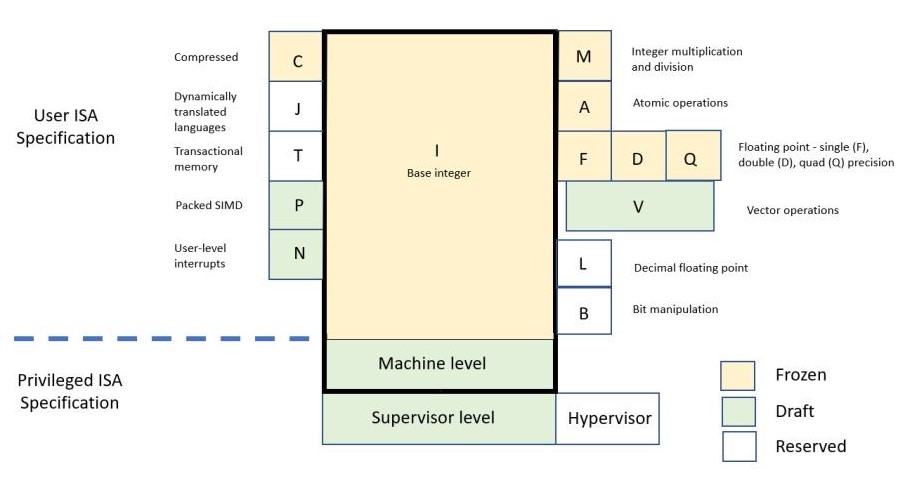

RISC-V is software; it is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. Compared with proprietary ISAs such as those from Arm, and Intel, RISC-V’s open-source nature brings potential benefits in terms of stability, scalability, and security (see the first FAQ in this series for a discussion of these characteristics). And unlike proprietary ISAs, the RISC-V ISA is provided under open source licenses that do not require fees to use.

There are multiple dimensions to be considered when discussing testing standards and tools for ISAs, such as RISC-V. RISC-V’s extensibility makes verification of compliance an important starting point of testing systems and devices to ensure compatibility. To streamline the compliance testing process, the RISC-V Compliance Framework Version 0.1 has been released. This framework compares arbitrary models against a reference signature and currently covers RV32IMC unprivileged spec only.

Work on Version 0.2 framework is underway, comparing two arbitrary models against each other (one of which can be a reference model), expanding the configurations covered, and automatically selecting tests according to the model configuration. Commercial testing compliance testing tools are also beginning to appear.

Imperas Software Ltd. offers a RISC-V compliance test suite for RV32I base RISC-V configuration. Developed in conjunction with the RISC-V Foundation’s Technical Committee task group for compliance, Imperas has achieved an almost 100% functional coverage of the instructions in the RISC-V ISA base specification known as RV32I.

Detailed verification and proof of compliance is the purpose of the OneSpin RISC-V Verification App. It is designed to address the needs of both care providers and core integrators. It leverages OneSpin’s advanced formal verification expertise for high-integrity processor applications to verify the implementation with minimal setup and runtime exhaustively. The solution’s core is the formalization of the RISC-V ISA as a set of SystemVerilog Assertions (SVA) using the OneSpin Operational Assertion approach.

Processor trace specification

Earlier this year, the RISC Foundation ratified the processor trace specification. The new standard trace encoder algorithm allows engineers and developers to see exactly what instructions a core is executing, step by step. The processor trace specification is expected to help debugging by revealing accurate and detailed traces of activity, with filtering capabilities to isolate the trace portions that matter.

With the processor trace specification ratified, trace IP developers, SoC integration engineers, and debug software developers have agreed on a highly efficient compressed standard for representing program flow on a RISC-V core.

RISC-V member companies Andes Tech, Blue Spec, Codasip, Esperanto, ETH Zurich, Seagate, SiFive, Syntacore, UltraSoC, Ventana MicroSystems, Western Digital, and others contributed to the ratification of the processor trace specification. The RISC-V Foundation’s Processor Trace Task Group is in the process of enhancing the trace ecosystem. It will propose plans to the newly formed Trace and Debug Steering committee for its consideration and guidance.

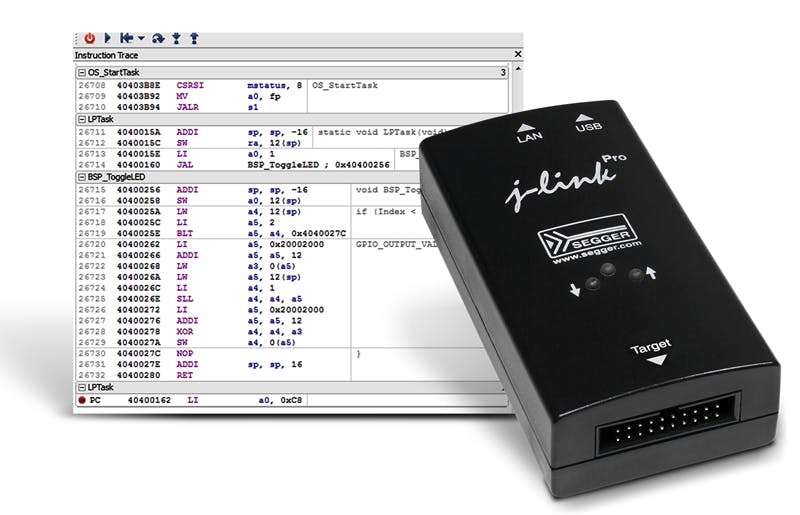

At about the same point in time that the RISC-V Foundation announced the new processor trace specification, SiFive announced SiFive Insight, a portfolio of trace and debug IP, software, and tools, to make the development of new SiFive RISC-V products efficient and simple. Observing device operation is critical for developing secure, efficient systems. These trace and debug features allow access to system state information and even modification to understand the system’s operational flow better. SiFive Insight can be implemented using tools from IAR Systems and Segger.

IAR offers the development toolchain IAR Embedded Workbench for RISC-V with support for trace as implemented by SiFive Insight, the industry’s first combined pre-integrated trace and debugs solution. IAR Embedded Workbench is a complete development toolchain including the highly optimizing IAR C/C++ Compiler and the feature-rich C-SPY Debugger. The software is complemented by native debugging and trace probes. The debug probe I-jet supports on-chip RAM buffered trace, in addition to fast JTAG/cJTAG/DAP debug and is complemented by the powerful trace probe I-jet Trace, which can live-stream trace information for code coverage and profiling purposes.

The new trace features include an updated trace control and a status window that provides developers with full control of all active settings and the application’s live trace status. The C-SPY Debugger will decode trace and calculate coverage and profiling as the application executes, populating the respective windows on the fly. This live update enables developers to monitor everything from the available trace buffer to the number of covered instructions. In addition, function profiling makes it possible to see and analyze timing information for an application’s functions. At the same time, code coverage analysis shows the percentage of code that has been executed down to a single instruction resolution. These combined capabilities offer a non-intrusive and easy-to-use code optimization tool.

SiFive Insight is compatible with Nexus 5001 trace specification standards and is fully supported by the SiFive Freedom Studio integrated developer environment (IDE). The Nexus 5001 Forum-Standard for a Global Embedded Processor Debug Interface (IEEE-ISTO 5001-2012) is an open industry standard that provides a general-purpose interface for the software development and debugs of embedded processors. Compatibility with Nexus 5001 trace also ensures compatibility with leading developer tools. SiFive cores support the recently ratified RISC-V Processor Trace standard. The RISC-V Foundation trace and debug working group is evaluating the Nexus 5001 trace as an additional standard to be ratified.

System integration testing

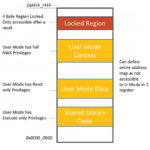

As an open ISA, RISC-V allows multiple approaches to implementing processor cores and can provide SoC developers with a range of sourcing options such as commercial IP suppliers, in-house developed cores, and open-source projects. The open ISA aspect of RISC-V also enables SoC developers to extend the ISA with customized instructions or extensions. This design flexibility brings the accompanying drawback that it multiplies the challenges of developing and implementing design verification and testing plans. Several vendors offer solutions.

Breker Verification Systems offers its RISC-V TrekApp, a complete, automated test content generator for RISC-V system integration testing. RISC-V TrekApp, the first solution to address the entire RISC-V system-on-chip (SoC) system integration problem, targets complex verification challenges and increases coverage by executing unpredictable corner-case scenarios without the need for manually developed test content. The TrekApp works with existing universal verification methodology (UVM) and SoC verification environments.

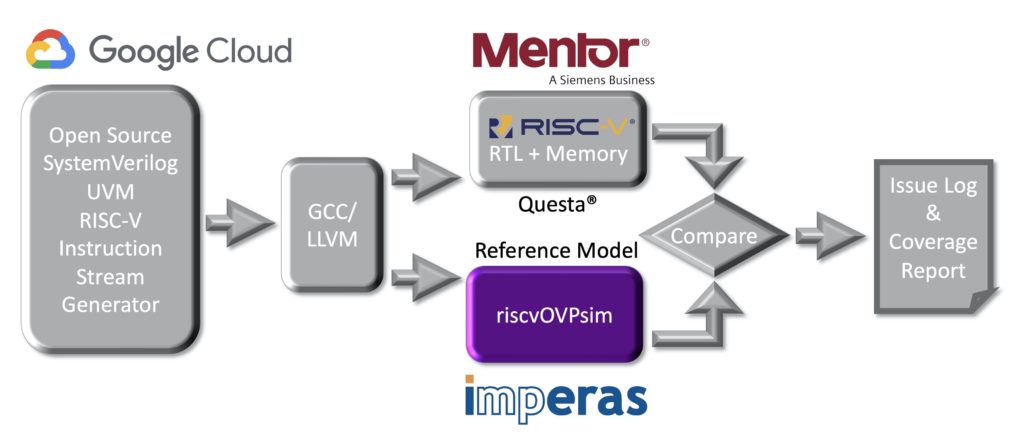

Imperas Software recently announced that the free riscvOVPsim RISC-V reference model and simulator has been updated and extended for RISC-V vector instructions and now supports coverage driven verification analysis. The base version of riscvOVPsim is available for free from a new GitHub site. An enhanced version includes an extensive RISC-V vector test suite also freely available for commercial use from Open Virtual Platforms.

Imperas collaborates with Mentor on the latest hardware Design Verification (DV) Flow for RISC-V processor implementations. It provides an easy to use reference methodology and is available to processor developers, users, and adopters across the RISC-V ecosystem.

Imperas, with assistance from Mentor, developed and enhanced the verification flow to compare the same corner case scenario for the functional behavior of the register-transfer level (RTL) under test, using the Questa platform environment against the golden reference model developed by Imperas. The latest development has been to expand the coverage analysis features to assist the DV engineers as they develop comprehensive test and verification plans for a new core implementation, custom extension, or initial assessment of a core prior to SoC integration.

The upcoming ratification of the RISC-V Vector instruction extension offers system designers broad flexibility to configure vector engines to support complex arithmetic operations required for applications involving linear algebra, such as high-performance computing, AI/ML, and VR/AR applications. With these latest enhancements to riscvOVPsim, software developers and system architects can start to explore RISC-V based solutions, while DV engineers can configure the models for test benches and test frameworks with coverage analysis.

DV testing for RISC-V supercomputer-on-chip

Esperanto Technologies has selected Valtrix Technologies’ STING DV Platform for design verification of its energy-efficient semiconductor solutions for AI/ML-based on the open standard RISC-V instruction set architecture. Esperanto plans to use STING for verifying the architectural compliance and functional correctness of its 7nm AI Supercomputer-on-Chip based on the high-performance ET-Maxion and energy-efficient ET-Minion microarchitectures.

STING, a highly versatile design verification tool developed by Valtrix Technologies, can be used to generate and execute different testing workloads (directed/random/algorithmic) on a device-under-test for verifying architectural compliance and testing its functionalities. The test methodology enables portability of stimulus simulations and in-circuit emulation across various FPGA and SoCs, resulting in a high degree of verification reuse and efficiency.

Functional safety and RISC-V

IAR Systems recently extended its tools offering for RISC-V by announcing a certified version of its development tools. The functional safety edition of IAR Embedded Workbench for RISC-V will be certified by TÜV SÜD according to the requirements of IEC 61508, the international umbrella standard for functional safety, as well as ISO 26262, which is used for automotive safety-related systems. In addition, the certification covers the international standard IEC 62304, which specifies life cycle requirements for the development of medical software and software within medical devices, and the European railway standards EN 50128 and EN 50657.

Functional safety certification for RISC-V will be available for the next version, 1.40, of IAR Embedded Workbench for RISC-V. The certification process is expected to be finalized in early 2021.

The first two FAQs in this series considered the performance capabilities of the RISC-V ISA, current risk factors in adopting RISC-V, and the emergence and evolution of testing standards and tools for RISC-V developers. RISC-V is modular and highly scalable; the next two FAQs will consider RISC-V-based ultra-low-power processing applications as well as high-performance applications such as ADAS, AI/ML, and even supercomputers.

References:

Extending SoC Design Verification Methods for RISC-V Processor DV, Mentor Graphics

Getting started with RISC-V verification, RISC-V Foundation

IAR Systems brings functional safety tools to RISC-V with certification for IEC 61508 and ISO 26262, IAR Systems

Nexus 5001 Forum™ Standard, Nexus 5001 Forum

RISC-V Foundation Announces Ratification of the Processor Trace Specification, RISC-V Foundation

Leave a Reply