![]() Lattice Semiconductor Corporation announces the availability of seven new modular IP cores for its award winning CrossLink FPGA product for increased design flexibility to support consumer, industrial and automotive applications. These modular IP cores offer the building blocks for customers to create their own unique video bridging solutions.

Lattice Semiconductor Corporation announces the availability of seven new modular IP cores for its award winning CrossLink FPGA product for increased design flexibility to support consumer, industrial and automotive applications. These modular IP cores offer the building blocks for customers to create their own unique video bridging solutions.

The mobile industry, through its demand for high volumes and exceptional performance, has created video components such as processors, displays, and sensors that are valued in other “mobile-influenced” markets. These markets demand cost-effective devices that bridge between MIPI® and other traditional or legacy display and camera interfaces.

“Our customers are asking for FPGAs with MIPI D-PHY capability to solve increasingly difficult video interface problems. Too often, they reach barriers with solutions that miss the mark on power efficiency, size and performance,” said Tom Watzka, product marketing manager at Lattice Semiconductor. “For more than a year, Lattice’s CrossLink devices and its portfolio of IP cores have delivered the tools needed to overcome these challenges. These new IP cores add to an already robust suite of tools to support quickly evolving intelligence at the edge applications.”

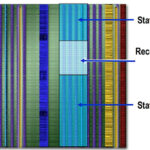

Announced in May 2016, the CrossLink product was designed to address barriers faced by the increasingly complex and dynamic video market. Lattice equipped designers with a new way to deliver low power and compact bridging solutions without compromising performance to deliver cutting-edge innovations for multiple growth markets including automotive, AR/VR and drones.

The new CrossLink modular IP cores include:

CSI-2/DSI D-PHY Receiver – Converts MIPI CSI-2/DSI data streams to parallel data

CSI-2/DSI D-PHY Transmitter – Converts parallel formatted data streams to MIPI CSI-2/DSI

FPD-LINK Receiver – Converts FPD-LINK video streams to pixel clock domain

FPD-LINK Transmitter – Converts Pixel Data Streams to an FPD-LINK video stream

SubLVDS Image Sensor Receiver – Converts SubLVDS image sensor video stream to pixel clock domain

Pixel to Byte Converter – Converts pixel format data to parallel byte format for D-PHY transmitter

Byte to Pixel Converter – Converts parallel byte format from a D-PHY receiver into pixel format

In addition, Lattice has included a 1:2 MIPI DSI Display Interface Bandwidth Reducer, which utilizes select modular IP cores above to bridge an input video stream into two streams or one lower resolution stream.

The newly expanded suite of CrossLink IP cores can be accessed here and are readily available in the Clarity Designer tool in Lattice’s Diamond software. CrossLink evaluation boards with the new IP cores are available now from Lattice and its distributors. To learn more, please visit www.latticesemi.com/CrossLink.

Leave a Reply