The number of FPGA manufacturers is relatively small so — like suppliers in any number of electronic components and systems markets — increased competition has lead to an even more increasing need to develop products with differentiating features. Now add in the IoT-inspired move from homogeneous to heterogeneous computing where we see intelligence being pushed to the edge of the network. Components built into edge nodes must be able to handle the required intelligence and processes. In addition, they must be lower power enough, cost-effective enough while taking into account cybersecurity and safety.

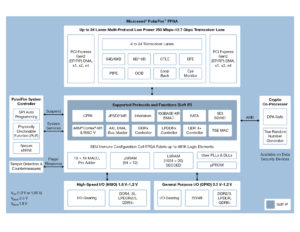

That, says, Shakeel Peera, senior director, SoC product marketing at Microsemi, is where FPGAs will be a “central part of the story” and where this semiconductor and systems company sees their new mid-range, cost-optimized FPGA playing. The non-volatile PolarFire FPGAs are designed to deliver the lowest power at densities up to 500K logic elements (LE) for communications, defense, and industrial markets.

where this semiconductor and systems company sees their new mid-range, cost-optimized FPGA playing. The non-volatile PolarFire FPGAs are designed to deliver the lowest power at densities up to 500K logic elements (LE) for communications, defense, and industrial markets.

Of the four major FPGA players, says Peera, two are fighting a nuclear war at the high end, and not necessarily gowning into adjacent markets and another is selling into the low-end consumer space. The central part of this market, he maintains, is being underserved and no one has a focused presence. “We feel no one is paying attention to this forgotten segment. We want to make FPGAs great again and we intend to fill the gap with PolarFire.”

“When you think of Flash FPGAs,” says Peera, “you don’t necessarily think cost-optimized. That’s because traditional Flash is not very scalable in submicron. We are using a less expensive 25nm process which lowers wafer cost and provides optimal yield. We’ve partnered with Cypress to optimize our proprietary Silicon-Oxide-Nitride Oxide-Silicon (SONOS) process which allows non-volatile memory elements to scale down more cost effectively and use smaller charge pumps than traditional Flash technology. A large die size also means more power consumption because you need more transistors. We use less transistors so we can offer lower power than even power-optimized FPGAs.”

PolarFire offers a low device static power of 26 mW for the 100K LE device, 90 mW at 10G low power transceiver lane, a 10mW (for 100K LE device) Flash Freeze mode that allows customers with portable power products to have the longest battery life without compromising on processing performance.

Gates, guns, and guards

According to the NSA, U.S. companies lose about $250 billion per year through intellectual property theft, with another $114 billion lost due to cyber crime, a number that rises to $338 billion when the costs of down time due to crime are taken into account. Peera says Microsemi is addressing this “greatest transfer of wealth in human history” by including a Secured Production Programming Solution (SPPS) that enables secured production programming of Microsemi FPGAs and SoCs by generating and injecting cryptographic keys and configuration bitstreams and controlling the number of devices programmed. This can prevent cloning, reverse engineering, malware insertion, leakage of sensitive intellectual property (IP), overbuilding, and other security threats.

“Cyber security is especially critical at the edge of the network where these FPGAs are particularly well suited,” says Preer. ”

Stepping it up with software

Unsurprisingly, designers are generally not comfortable migrating away from their FPGA comfort zone and the lack of tools is often the biggest barrier to entry. To ease the migration, Microsemi is also offering software tools aimed at making the transition to their FPGAs simpler. The Libero SoC Design Suite includes a number of tools to increase security, usability, and efficiency. The SmartDebug FPGA debugging suite slashes debugging and validation time by several weeks or months, says Peera. While PolarFire includes an integrated logic analyzer, the SmartDebug tool brings the equivalent of an oscilloscope inside the FGPGA.

“With the Liberto design suite, we tried to give everything the look and feel of environments designers are used to,” said Peera. “They can expect the same structure as other FPGA design tools.”

Features

- High-speed serial connectivity with built-in multi-gigabit multi-protocol transceivers from 250 Mbps to 12.7 Gbps

- Up to 481K logic elements consisting of a four-input look-up table (LUT) with a fracture-able D-type flip-flop

- Up to 33 MBs of RAM

- Up to 1480 18 x 18 multiply accumulate blocks with hardened pre-adders

- Integrated dual PCIe for up to x4 Gen2 endpoint (EP) and root port (RP) designs

- High-speed I/O (HSIO) supporting up to 1600 Mbps DDR4, 1333 Mbps DDR3L and 1333 Mbps LPDDR3/DDR3 memories with integrated I/O gearing

- General purpose I/O (GPIO) supporting 3.3 volts (V), built-in clock and data recovery (CDR) for serial gigabit Ethernet (SGMII), 1067 Mbps DDR3 and 1600 Mbps low-voltage differential signaling (LVDS) I/O speed with integrated I/O gearing logic

The PolarFire FPGA product family is shipping to early access customers now and samples for general availability will be offered in the second quarter of 2017.

Leave a Reply