RISC-V is an exciting and rapidly-emerging technology. RISC-V is software; it is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. So far, this FAQ series has looked at how “RISC-V is growing and offers stability, scalability, and security,” the “Growing availability of tools reducing the risk of using RISC-V,” and “RISC V for artificial intelligence machine learning and embedded systems.” This final FAQ considers the use of RISC-V in ultra-low power applications.

PULP Platform

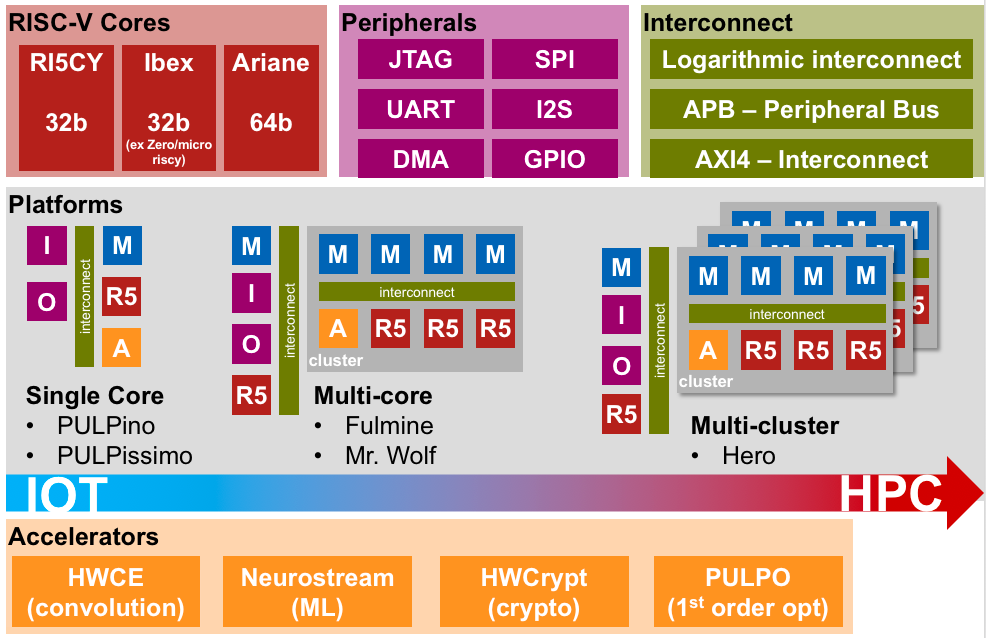

The Parallel Ultra Low Power (PULP) Platform started as a joint effort between the Integrated Systems Laboratory (IIS) of ETH Zürich and the Energy-Efficient Embedded Systems (EEES) group of the University of Bologna to explore new and efficient architectures for ultra-low-power processing.

PULP is developing an open, scalable hardware and software research and development platform to break the energy efficiency barrier within a power envelope of a few milliwatts, as well as satisfy the computational demands of IoT applications requiring flexible processing of data streams generated by multiple sensors, such as accelerometers, low-resolution cameras, microphone arrays, and vital signs monitors. PULP features:

- Efficient implementations of RISC-V cores. These include:

- 32-bit 4-stage core CV32E40P (formerly RI5CY)

- 64 bit 6-stage CVA6 (formerly Ariane)

- 32-bit 2-stage Ibex (formerly Zero-riscy)

- Complete systems based on:

- single-core micro-controllers (PULPissimo, PULPino)

- multi-core IoT Processors (OpenPULP)

- multi-cluster heterogeneous accelerators (Hero)

- Open-source SolderPad license

- a perpetual, worldwide, non-exclusive, no-charge, royalty-free, irrevocable license

- Rich set of peripherals

- I2C, SPI, HyperRAM, GPIO

PULP includes a state-of-the-art microcontroller system and a multi-core platform able to achieve leading-edge energy-efficiency and widely-tunable performance. Compared to single-core microcontroller units, a parallel ultra-low-power programmable architecture allows meeting the computational requirements of IoT applications without exceeding the power envelope of a few milliwatts typical of miniaturized, battery-powered systems.

PULP is an open-source platform. So far, PULP has released efficient 32- and 64-bit implementations based on the open-source RISC-V instruction set architecture, peripherals, and complete systems starting from simple microcontrollers to the state-of-the-art OPENPULP release, which sets a new bar for low-power multicore IoT processors. Additionally, PULP intends to support multiple application programming interfaces such as OpenMP, OpenCL, and OpenVX that allow agile application porting, development, performance tuning, and debugging.

PULP platform processors

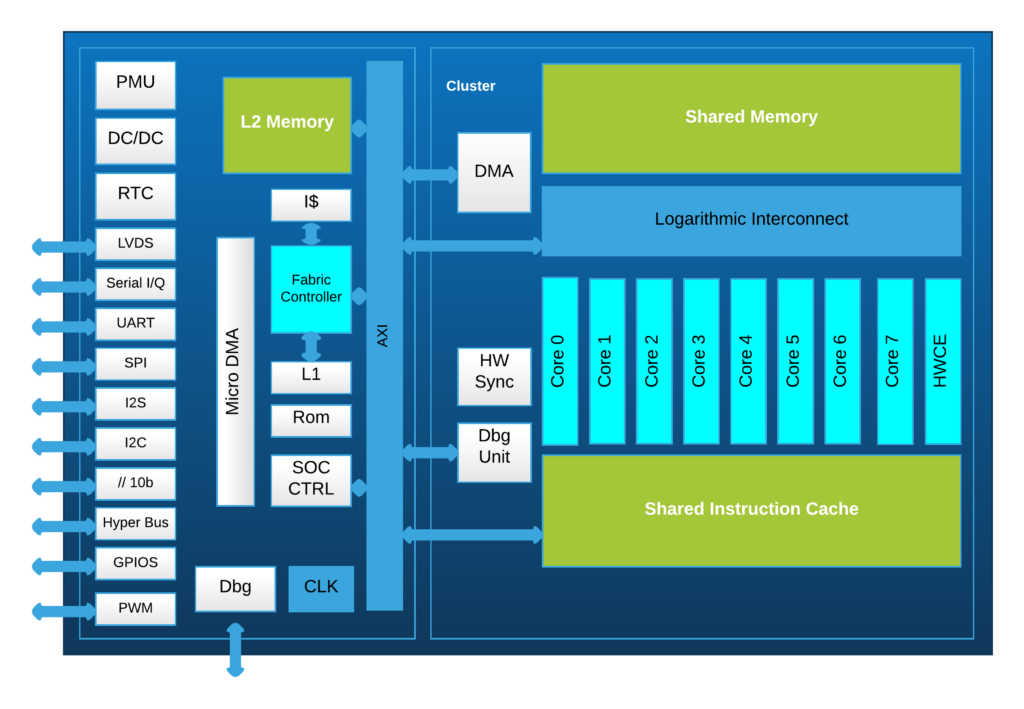

Several companies offer processors based on the open-source PULP platform. GreenWaves Technologies offers the ultra-low-power and high-performance GAP8 APs that enable AI in battery-powered IoT devices. GreenWaves is a key contributor to the RISC-V–based PULP open-source platform, which provides the foundation for its GAP8 processors. GAP8 is an IoT application processor that enables massive deployment of low-cost, battery-operated intelligent devices that capture, analyze, classify and act on the fusion of rich data sources such as images, sounds, radar signatures, and vibrations.

GAP8 is optimized to execute a large spectrum of image and audio algorithms, including convolution neural network inference and signal processing with extreme energy efficiency. GAP8 allows industrial and consumer product manufacturers to integrate signal processing, artificial intelligence, and advanced classification into new classes of battery-operated wireless edge devices for IoT applications, including image recognition, counting people and objects, machine health monitoring, home security, speech recognition, audio enhancements, consumer robotics, and smart toys.

The newest release of Renode, Antmicro’s open-source multi-node simulation framework, adds support for even more RISC-V platforms and CPUs, including the VEGAboard with RI5CY, a 32-bit RISC-V core originally created for the PULP platform. Renode’s board support includes UART and timer models and the Digilent Arty FPGA Evaluation Kit with LiteX and VexRiscv, a target to start working with the LiteX Build Environment.

LiteX support in Renode has been further upgraded with SPI, Control and Status, SPI Flash, and GPIO port peripheral models. LiteX is Antmicro’s choice for vendor-neutral, Linux- and Zephyr-capable soft SoC platforms and can support many internal and external use cases. Release 1.8 also adds support for Minerva, a 32-bit RISC-V soft CPU, which is now also available as a choice for the LiteX SoC.

Non-PULP low-power RISC-V processors

Not surprisingly, given the modularity and extensibility of RISC-V, there are numerous independent efforts to develop low-power RISC-V processors and extensions to the RISC-V ISA. One example of the latter is a demonstration by Codasip using the company’s Codasip Studio to develop a RISC-V ISA extension for ultra-low power IoT wireless signal processing. The resulting ISA extension was implemented on the Codasip Bk3, which has a single 3-stage pipeline architecture, providing a good balance between low power and performance, which reaches up to 3.1 CoreMark/MHz.

The Codasip project’s goal was to develop a simple ISA extension to support multiple wireless protocols while not increasing the power consumption of the Bk3 processor. The project resulted in an ISA with 13 instructions. It achieved zero incremental energy cost, has an efficient automatic gain control, and was demonstrated on BlueTooth, Sigfox, and LoRa wireless devices.

Huami recently unveiled a new AI chip for wearable devices. The Huami Huangshan-2(MHS002) is based on RISC-V architecture and is expected to enter mass production in the fourth quarter of 2020. The first wearable devices featuring the chip will arrive in 2021.

According to Huami, the new chip is faster and more energy-efficient than its predecessor, reducing overall power consumption by 50 percent. The energy improvements are realized with the help of an Always-On sensor mode and C2 co-processor. The Huangshan-2 arrives roughly a year and a half after the Huangshan No.1, which boasted a cardiac biometrics engine, an ECG, an ECG Pro, and an engine to monitor heart rhythm abnormalities.

Telink Semiconductor and Andes Technology recently introduced the new connectivity system on a chip (SoC) for Telink’s latest product line, the TLSR9 series. Powered by the 32-bit AndesCore D25F, the TLSR9 series is designed for the next generation of hearables, wearables, and high-performance IoT applications. Thanks to the companies’ partnership with IAR Systems, IoT designers will also have access to IAR’s Embedded Workbench (EW), a powerful development toolchain that supports flexible product development.

The Telink TLSR9 series is the latest addition to Telink’s line of complete connectivity solutions, and it is designed to maximize device performance and minimize time to market. The TLSR9 series is designed using the AndeStar™ V5 Instruction Set Architecture (ISA), which complies with the latest RISC-V technology.

The TLSR9 SoC features the D25F RISC-V processor and is the world’s first SoC that adopts a RISC-V DSP/SIMD P-extension, which is designed for a variety of mainstream audio, wearables, and IoT development needs. The D25F has an efficient five-stage pipeline and delivers 2.59 DMIPS/MHz and 3.54 CoreMark/MHz performance. By supporting the RISC-V P-extension (RVP), the D25F significantly increases efficiency for small-volume data computation and makes compact AI/ML applications possible on edge devices.

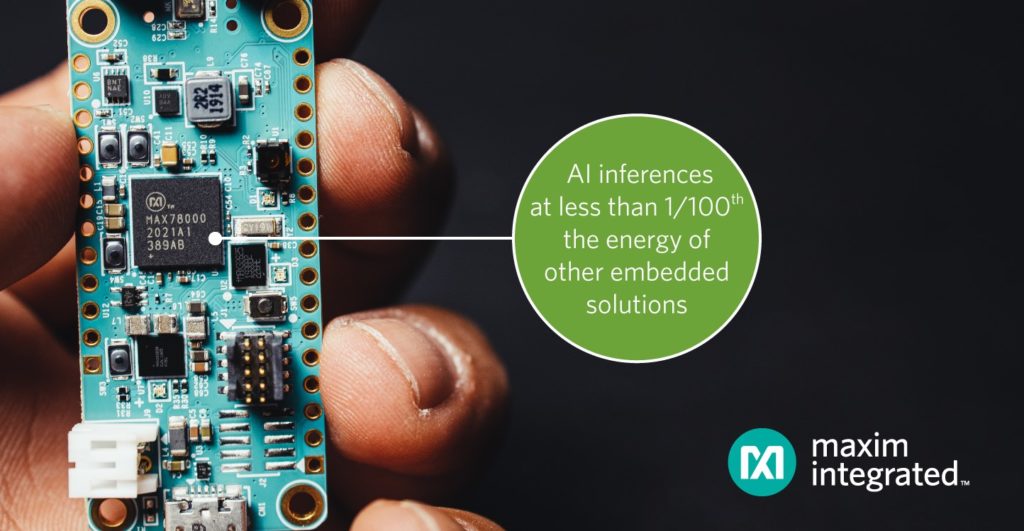

The MAX78000 low-power neural network accelerated microcontroller from Maxim Integrated Products combines a convolutional neural network (CNN) and RISC-V core with an Arm Cortex processor. This combination of capabilities moves AI to the edge without performance compromises in battery-powered IoT devices. Executing AI inferences at less than 1/100th of the energy of software solutions significantly improves run-time for battery-powered AI applications while enabling complex new AI use cases.

At the heart of the MAX78000 is specialized hardware designed to minimize CNN’s energy consumption and latency. This hardware runs with minimal intervention from any microcontroller core, making operation streamlined. To get data from the external world into the CNN engine efficiently, customers can use one of the two integrated microcontroller cores: the ultra-low-power Arm Cortex-M4 core or the even lower power RISC-V core.

RISC-V is growing and offers stability, scalability, and security. This series of FAQs have discussed how RISC-V is becoming more commercially attractive due to recent developments in design and validation tools. There is also a growing selection of RISC-V-based devices optimized for specific applications such as the IoT and wearables, embedded systems, artificial intelligence, machine learning, virtual reality, augmented reality, and military and aerospace systems. RISC-V is an emerging technology that most designers should follow and become increasingly familiar with.

References

A RISC-V ISA Extension for Ultra-Low Power IoT Wireless Signal Processing, Codasip

RISC-V, Wikipedia

The PULP Platform, PULP Platform

Leave a Reply