Avery Design Systems announced that its fully-tested Verification IP (VIP) for 800Gbps Ethernet can now be used to perform virtual network co-simulation for the full layer Ethernet 2-7 network stack. The combination of the VIP and a virtual co-simulation/co-emulation system enables the running of full hardware/software system verification on pre-silicon SoC RTL and software integrations. […]

averydesignsystemsinc

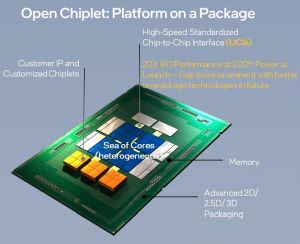

Verification support for new UCIe standard accelerates adoption of chiplet interconnect protocol

Support for the new UCIe (Universal Chiplet Interconnect Express) standard provides an efficient approach to enable design and verification engineers to leverage the recently-introduced standard for die-to-die interface connectivity. Avery’s offering includes high-quality models and test suites that support pre-silicon verification of systems using UCIe. As part of the support for the standard, Avery Design […]

Functional verification now handles CAN XL, TSN Ethernet 1/10G networking SoCs

Design and verification of automotive SoCs that utilize the emerging CAN XL and TSN Ethernet 1/10G networking and control protocols integrate CAST’s validated design IP for both standards with Avery’s verification IP (VIP) that streamlines the design and verification process to an ensure higher quality designs as well as compliance with the standards. The new […]

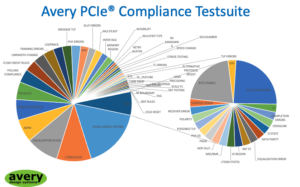

PCIe 6.0 verification IP enables advanced debug and compliance checking

Avery Design Systems Inc. announced the availability of major updates to the company’s flagship PCI Express (PCIe) 6.0 and PIPE 6.0 VIP solution. Avery unveiled the solution at the PCI-Sig DevCon event this week. The solution supports the latest features and capabilities in the high-speed interconnect protocol, including a doubling of data rates compared to PCIe […]