Rambus Inc. announced the availability of its state-of-the-art Gen4 DDR5 Registering Clock Driver (RCD) which began sampling to the major DDR5 memory module (RDIMM) manufacturers in the fourth quarter of 2023. The Rambus Gen4 RCD boosts the data rate to 7200 MT/s, setting a new benchmark for performance and enabling a 50% increase in memory bandwidth over […]

rambusinc

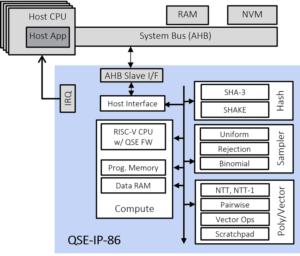

IP engine integrated into RoT or embedded secure element in SoCs and FPGAs

Rambus Inc. announced the availability of a Quantum Safe Engine (QSE) for integration into hardware security elements in ASICs, SoCs, and FPGAs. Quantum computers will enable adversaries to break current asymmetric encryption, placing important data and assets at risk. The Rambus QSE IP core uses NIST-selected quantum-resistant algorithms to protect valuable data centers and government hardware […]

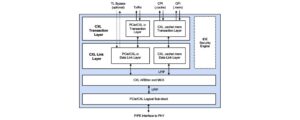

PCIe 5.0 controllers now available with zero-latency integrated IDE

Rambus Inc. announced Compute Express Link (CXL) 2.0 and PCI Express (PCIe) 5.0 controllers now available with integrated Integrity and Data Encryption (IDE) modules. Delivering security at speed in CXL is critical to solving the bandwidth bottleneck in data center infrastructure. IDE monitors and protects against physical attacks on CXL and PCIe links. CXL requires […]

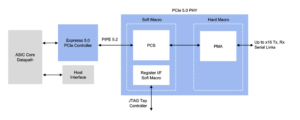

PCIe 5.0 digital controller supports up to 32 GT/sec data rates

Rambus Inc. announced that Rambus has demonstrated its PCI Express (PCIe) 5.0 digital controller IP on leading FPGA platforms. PCIe 5.0 performance at 32 GT/s in FPGAs using a soft controller is an industry first, and another demonstration of technical leadership from Rambus. This capability expands the use models of FPGAs by enabling multi-instance, switching, and bridging […]

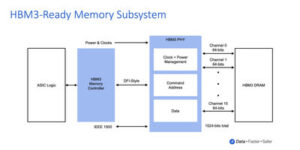

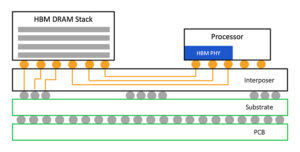

HBM3-ready memory interface subsystem includes PHY, digital controller

Rambus Inc. announced the Rambus HBM3-ready memory interface subsystem consisting of a fully integrated PHY and digital controller. Supporting breakthrough data rates of up to 8.4 Gbps, the solution can deliver over a terabyte per second of bandwidth, more than double that of high-end HBM2E memory subsystems. With a market-leading position in HBM2/2E memory interface deployments, Rambus is […]

AI applications and emerging computing architectures – Virtual Conversation (part 1 of 2)

Hosted by Jeff Shepard, EE World has organized this “virtual conversation” with Gary Bronner (GB), Senior Vice President with Rambus Labs. Mr. Bronner has generously agreed to share his experience and insights into AI applications and emerging computing architectures. JS: What is usually the biggest challenge designers face when first using artificial intelligence? GB: One […]

PHY for extra short reach/ultra short reach channels works on 7-nm chip process

Rambus Inc. announced it has expanded its portfolio of high-speed interface IP on TSMC’s industry-leading 7nm process with the addition of its silicon-demonstrated 112G XSR/USR PHY. Offering unmatched power and area efficiency for next-generation applications, the 112G XSR/USR PHY is a critical enabler of chiplet and CPO architectures for data center, networking, 5G, HPC and AI/ML […]