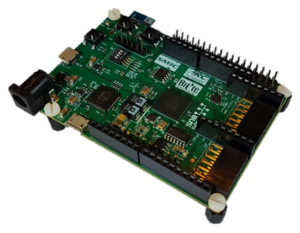

Synopsys, Inc. announced the new DesignWare ARC IoT Development Kit to accelerate software development and debug of ARC processor-based system-on-chip (SoC) designs. The ARC IoT Development Kit includes a silicon implementation of the ARC Data Fusion IP Subsystem as well as a rich set of peripherals commonly used in IoT designs such as USB, I3C and PWM. […]

synopsys

Real-time voice-enhancement tech works with DSP design software

Synopsys, Inc. and Alango Technologies today announced that Alango Technologies’ Voice Enhancement Package (VEP) software has been optimized for Synopsys’ DesignWare® ARC® Data Fusion IP Subsystem. The VEP is a suite of real-time software DSP technologies designed for improving speech recognition performance in voice-controlled multimedia devices. The ARC Data Fusion IP Subsystem is a highly integrated hardware and software IP […]

Logic libraries, embedded memory IP covers 40-nm ultra-low power, 40-nm low-power eFlash designs

Synopsys, Inc. announced its collaboration with TSMC to develop foundry-sponsored DesignWare Foundation IP, including logic libraries and embedded memories, for TSMC’s 40-nanometer (nm) ultra-low power (ULP) eFlash and 40-nm low-power (LP) eFlash processes. Synopsys’ Foundation IP on TSMC’s 40-nm eFlash processes implements unique features that enable designers to reduce power consumption for IoT designs. The logic […]

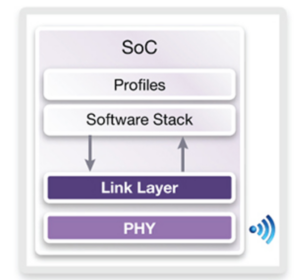

Low-energy PHY IP achieves Bluetooth 5 qualification

Synopsys, Inc. announced that the silicon-proven DesignWare Bluetooth Low Energy Link Layer IP and PHY IP in industry-standard 40-nanometer (nm) and 55-nm processes have achieved Bluetooth 5 qualification and have been declared compliant by the Bluetooth Special Interest Group. Achieving qualification ensures the robustness of the IP and that it functions as expected within a system-on-chip (SoC). […]

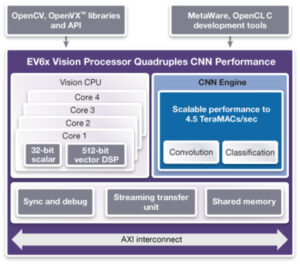

Processors optimize vision software for deep learning applications

Synopsys, Inc. announced a collaboration with Morpho, Inc. to optimize Morpho’s computational photography software for Synopsys’ DesignWare EV6x Vision Processors. Morpho’s Scene Classifier image classification technology uses deep learning algorithms to analyze visual input and automatically apply tags for classification, searchability and organization. Morpho is optimizing their software to take advantage of the EV6x Vision Processors’ […]

High-bandwidth memory 2 IP includes PHY, controller and verification facilities

Synopsys, Inc. introduced its complete DesignWare High Bandwidth Memory 2 (HBM2) IP solution consisting of controller, PHY and verification IP, enabling designers to achieve up to 307 GB/s aggregate bandwidth, which is 12 times the bandwidth of a DDR4 interface operating at 3200 Mb/s data rate. In addition, the DesignWare HBM2 IP solution delivers approximately ten times better […]

Chip design IP emphasizes software integrity and security

Synopsys, Inc. announced key updates to its Software Integrity Platform that are designed to help companies build security and quality into their software while reducing time-to-market. In the era of digital transformation, building secure and reliable software is challenged by the rapid, complex and diverse nature of development cycles. The latest updates to the Synopsys Software Integrity Platform […]

Vision processors now handle high video resolution and frame rates for high-performance embedded apps

Synopsys, Inc. announced that it has enhanced the convolutional neural network (CNN) engine in its DesignWare EV6x Vision Processors to address the increasing video resolution and frame rate requirements of high-performance embedded vision applications. The CNN engine delivers up to 4.5 TeraMACs per second when implemented in 16-nanometer (nm) FinFET process technologies under typical conditions, four times […]

Chip design IP now works with 7-nm Leading-Performance (7LP) FinFET process

Synopsys, Inc. today announced the enablement of the Synopsys Design Platform and DesignWare® Embedded Memory IP on GLOBALFOUNDRIES 7-nm Leading-Performance (7LP) FinFET process technology. Synopsys and GF collaboration on the new process addressed several new challenges specific to the 7LP process. This process is expected to deliver 40 percent more processing power and twice the area scaling […]

Verification IP, source-code test suite works with ARM AMBA 5 Coherent Hub Interface Issue B

Synopsys, Inc. today announced the availability of its Verification IP (VIP) and source code test suite for ARM® AMBA® 5 Coherent Hub Interface (CHI) Issue B. Synopsys VC VIP for AMBA CHI has been widely adopted by SoC leaders for successful verification closure and tape out of coherent subsystems and interconnects. Synopsys VIP for the latest AMBA CHI Issue B specification enables […]