Synopsys, Inc. and Samsung Foundry announced the release of a validated automotive reference flow to streamline SoC hardware design for in-system test, implementation, verification, timing, and physical signoff for ISO 26262 compliance. This reference flow is targeted for automotive safety integrity level (ASIL) D autonomous driving and advanced driver-assistance systems (ADAS) applications. In close collaboration with […]

synopsysinc

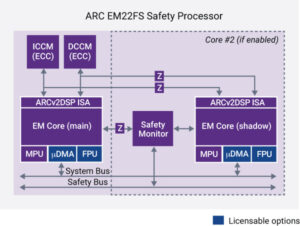

Functional safety processor meets requirements for ISO 26262 ASIL D compliance

Synopsys, Inc. today announced that the DesignWare ARC EM22FS Functional Safety Processor has achieved certification for full ISO 26262 automotive safety integrity level (ASIL) D compliance, meeting both random hardware fault detection and systematic functional safety development flow requirements. The full compliance allows companies to accelerate the development and assessment of their automotive safety-critical SoCs for random […]

Silicon design kit optimized for high-bandwidth memory/PCIe/ethernet connectivity

Synopsys, Inc. announced its collaboration with GLOBALFOUNDRIES to develop a broad portfolio of DesignWare IP for GF’s 12LP+ FinFET solution, including USB4/3.2/DPTX/3.0/2.0, PCIe 5.0/4.0/2.1, die-to-die HBI and 112G USR/XSR, 112G Ethernet, DDR5/4, LPDDR5/4/4X, MIPI M-PHY, Analog-to-Digital Converter, and one-time programmable (OTP) non-volatile memory (NVM) IP. The DesignWare IP is optimized to meet the high-bandwidth memory throughput […]

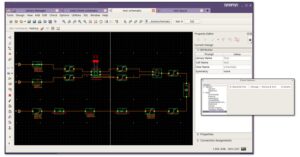

Unified electronic/photonic design platform speeds photonic IC design tasks

Synopsys, Inc. introduced its OptoCompiler solution for photonic integrated circuit (PIC) design, layout implementation and verification. OptoCompiler is the industry’s first unified electronic and photonic design platform, combining mature and dedicated photonic technology with Synopsys’ industry-proven electronic design tools and methods to enable engineers to produce and verify complex PIC designs quickly and accurately. By providing schematic-driven […]

Low-power GNSS IP speeds IoT modem development

Synopsys and Nestwave today announced a collaboration to combine Nestwave’s softcore GPS navigation IP with the Synopsys DesignWare ARC IoT Communications IP Subsystem for a complete low-power global navigation satellite systems (GNSS) solution for integration into IoT modems. The collaboration will provide designers with a power-efficient, high-accuracy GPS solution for battery-operated devices without the additional cost of […]

Multi-die IC design software keys on Chip-on-Wafer-on-Substrate efforts

Synopsys and TSMC have collaborated to deliver certified design flows for advanced packaging solutions using the Synopsys 3DIC Compiler product for both silicon interposer based Chip-on-Wafer-on-Substrate (CoWoS-S) and high-density wafer-level RDL-based Integrated Fan-Out (InFO-R) designs. 3DIC Compiler provides packaging design solutions required by today’s complex multi-die systems for applications like high-performance computing (HPC), automotive and […]

USB4 IP covers controllers, routers, PHYs

Synopsys today introduced the industry’s first complete DesignWare USB4 IP solution consisting of controllers, routers, PHYs, and verification IP. The DesignWare USB4 IP operates at up to 40 Gbps, which is twice the maximum data rate of USB 3.2 and is backward compatible with USB 3.x and USB 2.0 systems. The DesignWare USB4 IP supports […]

Tape-outs for SoCs aid early adopters of Arm mobile processor IP

Synopsys announced that Synopsys and Arm have collaborated to enable tapeouts of optimized system-on-chips (SoCs) for early adopters of Arm’s latest mobile processor IP, including Arm Cortex-A78 and Cortex-X1 CPUs, and Mali-G78 GPU. A range of Synopsys solutions, including the Synopsys Fusion Design Platform, Verification Continuum Platform, and DesignWare Interface IP, were used in the design of […]

Design software accelerates development of SoCs for high-end cloud computing, AI apps

Synposys announced the industry’s broadest portfolio of high-quality IP on TSMC’s 5nm process technology for high-performance computing system-on chips (SoCs). The DesignWare IP portfolio on the TSMC process, encompassing interface IP for the most widely used high-speed protocols and foundation IP, accelerates development of SoCs for high-end cloud computing, AI accelerators, networking and storage applications. The combination […]

Chip-design compiler keys on 2.5, 3D multi-die system-in-a-package developments

Synopsys introduced its 3DIC Compiler platform to transform the design and integration of complex 2.5 and 3D multi-die system in a package. It provides an unprecedented fully integrated, high-performance, and easy-to-use environment, offering architectural exploration, design, implementation, and signoff with signal, power, and thermal integrity optimizations, all in one solution. With 3DIC Compiler, IC design […]