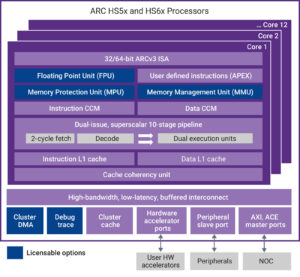

Synopsys announced the new DesignWare ARC HS5x and HS6x processor IP families for high-performance embedded applications. The 32-bit ARC HS5x and 64-bit HS6x processors, available in single-core and multicore versions, are implementations of a new superscalar ARCv3 Instruction Set Architecture (ISA) and deliver up to 8750 DMIPS per core in 16-nm process technologies under typical conditions, making them […]

synopsysinc

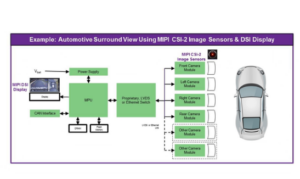

Chip design software promotes high-throughput camera and display SoC development

Synopsys announced it is expanding its MIPI camera and display IP portfolio with the DesignWare MIPI C-PHY/D-PHY IP for a range of FinFET processes. The silicon-proven C-PHY/D-PHY IP is compliant with the MIPI C-PHY v1.2 and D-PHY v2.1 specifications for a low-risk solution targeting high-resolution imaging and display SoCs. In addition, the C-PHY/D-PHY meets the stringent functional […]

Ethernet 800G Verification IP targets next-generation networking systems

Synopsys, Inc. announced the availability of the industry’s first verification IP (VIP) and Universal Verification Methodology (UVM) source code test suite for Ethernet 800G. As the requirements for increased bandwidth to support video-on-demand, social networking and cloud services continues to rise, Synopsys VC VIP for Ethernet 800G, based on the Ethernet Technology Consortium (ETC) specification, enables […]

Physically aware RTL design system halves SoC implementation cycle

Synopsys announced the immediate availability of RTL Architect, an innovative product that signifies a shift-left for RTL design closure. Synopsys RTL Architect is the industry’s first physically aware RTL design system, which reduces the SoC implementation cycle in half and delivers superior quality-of-results (QoR). RTL teams are increasingly faced with the challenges of rapidly exploring […]

Security testing software development tool analyzes open source, proprietary code

Synopsys, Inc. announced that on Feb. 18 it will release a major update to the Polaris Software Integrity Platform to extend its static application security testing (SAST) and software composition analysis (SCA) capabilities to the developer’s desktop through the native integration of the Code Sight IDE plugin. These capabilities, the first of their kind, will enable […]

Software development platform reduces noise, reduces memory footprint in SoC designs

Synopsys announced general availability of the VC SpyGlass RTL Static Signoff platform, part of the Synopsys Verification Continuum platform, which builds on the proven SpyGlass technology. The VC SpyGlass platform with multi-core support increases performance by 3X with half the memory footprint. The next-generation platform is enhanced with machine learning technology to reduce noise by […]

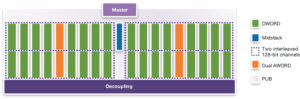

HBM2E PHY IP operates at 3.2 Gbps

Synopsys announced it has delivered silicon-proven HB M2E PHY IP operating at 3.2 gigabits per second (Gbps), addressing high throughput requirements of advanced graphics, high-performance computing and networking SoCs. Verified on TSMC’s Chip-on-Wafer-on-Substrate (CoWoS) advanced packaging technology, Synopsys’ DesignWare HBM2E PHY IP offers a micro-bump array that adheres to the JEDEC HBM2E SDRAM standard for the […]

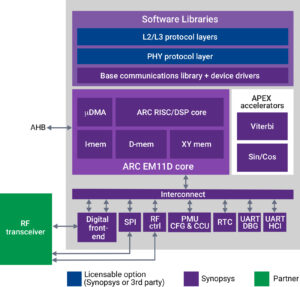

Ultra-low bandwidth wireless IoT platform combines processor, hardware accelerators, dedicated peripherals, RF interface

Synopsys launched its new DesignWare ARC IoT Communications IP Subsystem, an integrated hardware and software solution that combines Synopsys’ DSP-enhanced ARC EM11D processor, hardware accelerators, dedicated peripherals, and RF interface to deliver efficient DSP performance for ultra-low bandwidth wireless IoT (NB-IoT) applications, such as machine to machine communication. The ARC IP Subsystem includes SPI and […]

Dev kit accelerates high-performance SoC development

Synopsys announced availability of the DesignWare ARC HS4x/4xD Development Kit to accelerate software development for the ARC HS4x/4xD family of high-performance processor IP. The ARC HS4x/4xD Development Kit is a ready-to-use software development platform with support for the Linux kernel and access to the embARC open-source software packages on the embARC website, enabling designers to start software […]

BLE audio codec targets power-sensitive audio/voice apps

Synopsys announced the availability of the Bluetooth LE Audio LC3 Codec optimized for Synopsys’ DesignWare ARC EM DSP and HS DSP processor IP. The LC3 codec is an important feature of Bluetooth LE Audio, the soon-to-be-released next-generation audio standard defined by the Bluetooth Special Interest Group (SIG) that enables system-on-chip (SoC) designers to efficiently implement […]