The versatility of the RISC-V instruction set architecture (ISA) can be seen in the breadth of 5G applications using the technology. Examples include a complete 5G base station system-on-chip (SoC), a 5G small cell distributed unit (DU) SoC, a recurrent neural network (RNN) IC optimized for 5G radio resource management, even handsets are under development that include RISC-V cores.

In one recent development, a highly integrated and programmable 5G modem processor based on a RISC-V reference design was announced. This SoC is compliant with OpenRAN (or O-RAN) standards for open, interoperable Radio Access Network (RAN) solutions using software defined cores. Compared with the 100W of power consumed by a proprietary Intel Xeon-based solution, this RISC-V-based SoC consumes 10W and is claimed to reduce the base station’s total cost of ownership up to 50%.

An important part of the new SoC design was developing about 100 new custom instructions added to the already existing vector extension in the RISC-V instruction set architecture (ISA). The new instructions optimize the vector extension to accelerate the computationally complex mathematics needed to implement 4G and 5G signal processing and communications protocols.

The base station SoC is built using a RISC-V core license from Andes Technology to deliver a fully open and programmable 5G platform with integrated artificial intelligence (AI). The final design extends and customizes the RISC-V instruction set architecture (ISA) to achieve novel performance, features, and power profiles unmet by previous solutions for the wireless infrastructure.

Since the SoC includes extensive vector processing extensions, it is also well-suited to perform AI, and machine learning (ML) functions. The RISC-V cores have excess processing capacity that can be employed for ML activities. The cores can offload the processing of ML activities when idle. The cores can even be partitioned between 4G/5G and ML workloads distributed on a quality of service (QoS) managed basis. Designers using the SoC have full C/C++ access to the core, making it more flexible and programmable than other base station solutions. In addition to 4G/5G base stations, the SoC is expected to find applications in factory automation, industry 4.0, and robotics.

RISC-V for 5G O-RAN small cells

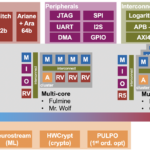

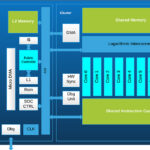

An AndesCore RISC-V 32-bit core with integrated peripherals was central to developing a 5G small cell distributed unit (DU) SoC. The compact size of the RISC-V cores allows the DU to pack 32 cores into the O-RAN SoC in two clusters, providing flexibility and data throughputs at line rates up to 25 Gbps for packet header processing. According to Picocom, the developer of the DU, using clusters of small RISC-Vs is more efficient than using a small number of larger cores. This clustered RISC-V approach supports maximum flexibility to cope with future 5G NR standards changes while delivering high performance in a very demanding application.

5G systems use orthogonal frequency-division multiple access (OFDMA) protocols. In such a system, data is transmitted in slots that can range in size from 0.125 to 0.25 ms. The scheduling of the traffic carried in these slots is a critical activity. Efficient 5G base stations are being designed and deployed to handle large numbers of users and support several separate mobile operators. Each operator may require its own software. As a result, managing the radio resources in a 5G cell site is a complex process.

Neural networks for 5G radio resource management

Radio resource management (RRM) for 5G new radio is complex. It is necessary to maximize utilization of the available frequency bands, especially under highly heterogeneous traffic (e.g., tiny sensor-nodes vs. mobile routers), and rapidly varying radio signal propagation conditions. To be meaningful, RRM has to be executed in a matter of milliseconds; otherwise, QoS can suffer. The diversity of 5G application scenarios impose strict requirements on RRM. Those applications include:

- very high reliability and low-latency for autonomous vehicles,

- very high bandwidth for video telephony and virtual reality, and

- machine-to-machine communication for the massive Internet of Things.

FPGAs can be used to deal with the necessary resource allocation algorithms required to distribute limited resources (e.g., frequency bands, transmit power, data rates) to mobile clients efficiently. Unfortunately, FPGAs cost too much to be used in the massive and dense deployments needed by 5G networks. To address this need, a RISC-V-based accelerator with recurrent neural network (RNN) specific extensions has been proposed for RRM applications. The proposed solution includes both hardware optimization and software optimization.

The extensions maintain backward compatibility with the baseline RISC-V ISA and have a minimal overhead (3.4%) in the area, and the length of the longest path is not changed. This solution is flexible and supports performance improvements over a quite diverse set of RNNs used for various RRM tasks. An order of magnitude improvement in energy efficiency (10x) and overall performance (15x) is achieved compared with the basic RISC-V ISA over a range of RNN configurations.

RISC-V handsets

The following are three examples of efforts to develop RISC-V-based handsets. While these activities are not solely focused on 5G, they point to the future development of RISC-V-based 5G handsets.

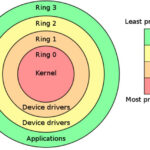

Precursor is a pocket-sized device and open hardware development platform for secure, mobile computation and communication. It includes a built-in display, a physical keyboard, and an internal battery while remaining smaller and lighter than the average smartphone. Precursor was built for use on the road. It is powered by an FPGA-hosted, soft-core System-on-Chip (SoC), and it gives developers the freedom to inspect, verify, and customize nearly every aspect of its operation. Precursor is built around a Xilinx XC7S50 primary System on Chip (SoC) FPGA: L1 speed grade for longer battery life and 100 MHz VexRISC-V, RV32IMAC + MMU, 4k L1 I/D cache.

The VexRISC-V an FPGA optimized RISC-V ISA implementation based on the RV32IM instruction set that does not use any vendor-specific IP blocks or primitives. As used in the Precursor platform, it includes the optional MMU.

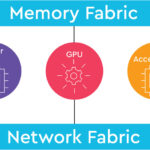

Several development teams are working on running the Android open source project (AOSP) operating system on RISC-V hardware. One effort is led by T-Head, the business entity of Alibaba specializing in semiconductors, which has ported Android 10 onto its in-house RISC-V hardware, an SoC that includes a XuanTie C910 core (RISC-V 64).

The SoC has integrates a GPU with 3 XuanTie C910 cores (RISC-V 64) and 1 GPU core. This SoC can provide 4K JPEG decoding and supports several high-speed interfaces and peripherals for data transfers, including 3D graphics and multimedia processing.

Finally, the Debian operating has been ported to the RISC-V architecture. Debian is a secure and stable Linux-based operating system. It’s being used on a range of devices, from laptops and desktops to servers. Mobian, a spinoff of Debian developed for mobile handsets, was launched in May 2020. The PinePhone is a Linux-based handset based on Mobian. While the PinePhone is based on an ARM processor, Debian has been ported to RISC-V opens the door for designers to develop RISC-V handsets based on Mobian.

Summary

As shown, RISC-V is being used and developed for a range of 5G applications, including a complete 5G base station system-on-chip (SoC), a 5G small cell distributed unit (DU) SoC, a recurrent neural network (RNN) IC optimized for 5G radio resource management, even handsets are under development that include RISC-V cores. The uses of RISC-V are expected to continue to expand into an increasing number of 5G applications.

References

Extending the RISC-V ISA for Efficient RNN-based 5G Radio Resource Management, Arxiv

Mobian Project, Mobian

Precursor, Crowd Supply

Leave a Reply