Microsemi Corporation today announced it is the first field programmable gate array (FPGA) provider to offer a comprehensive software tool chain and intellectual property (IP) core for RISC-V designs. The company’s RV32IM RISC-V core is available for Microsemi’s IGLOO™2 FPGAs, Sma

Microsemi Corporation today announced it is the first field programmable gate array (FPGA) provider to offer a comprehensive software tool chain and intellectual property (IP) core for RISC-V designs. The company’s RV32IM RISC-V core is available for Microsemi’s IGLOO™2 FPGAs, Sma

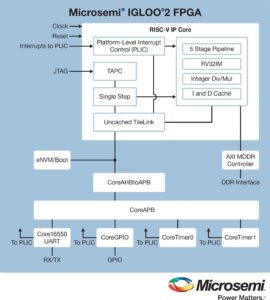

Microsemi’s new RV32IM RISC-V core, developed in collaboration with SiFive, enables customers to design with an open instruction set architecture (ISA), enabling complete portability and a more secure processor architecture governed by a permissive BSD license. RISC-V is a new ISA which is now a standard open architecture under the governance of the RISC-V Foundation. RISC-V offers a compelling soft processor solution for Microsemi’s low power, reliable, secure FPGAs. The RV32IM RISC-V core unleashes a new generation of innovation for embedded designers. Now engineers can rely on an open ISA, without being tied to a single vendor and leverage open source tools and hardware. Never before has a processor allowed designers to inspect, modify, adapt, collaborate and migrate their design to the best platform for their product. Microsemi’s low power FPGAs with proven security and embedded flash are a natural fit for this new paradigm.

“Our IGLOO2, SmartFusion2 and RTG4 devices are the ideal FPGAs to build RISC-V core onto, as we offer up to 50 percent lower power consumption with proven security for customers’ IP,” said Venki Narayanan, senior director of software and systems engineering for Microsemi’s SoC Products Group. “RISC-V is a great fit for implementing clean-slate processor capabilities for security, trust and reliability which are central to Microsemi’s solutions. We will continue our leadership position in this technology by further investing in this architecture to ensure customers have long-term roadmap support.”

Customers seeking to develop customized devices can now initiate their design into a Microsemi FPGA and bring their solution to market quicker. The combination of Microsemi’s IGLOO2 FPGA, SmartFusion2 SoC FPGA or RTG4 FPGA and its Libero SoC Design Suite create an ideal platform to target a RISC-V core for many embedded applications and is easy to implement with regard to size and power. The lower power and security of Microsemi’s FPGA families provides a sound architecture for customers seeking to protect their IP and ensure long-term support for their designs in the industrial, defense, secur

The new RV32IM RISC-V core is especially compelling for applications such as safety and security, as the register transfer level (RTL) source code is available for inspection. For example, customers can verify the security of the processor themselves, which is not possible with other processors, as they have closed architectures. In safety-critical applications, as customers can run multiple RISC-V cores to ensure if one fails there is a redundant core to take over.

“We are very excited Microsemi is releasing a RISC-V intellectual property core for its IGLOO2, SmartFusion2 and RTG4 FPGAs,” said Rick O’Connor, executive director of the RISC-V Foundation. “The complete Linux-based toolchain that the company is providing will enable a broad range of customers to develop RISC-V cores in Microsemi FPGAs. I applaud Microsemi’s leadership in introducing this comprehensive RISC-V platform and the foundation looks forward to working with the company to explore future advancements.”

Through Microsemi’s early involvement in the creation of the RISC-V Foundation, the company has an established leadership role in the emerging standard and ecosystem and is working closely with the nonprofit to ensure the ISA becomes an industry standard for a wide variety of computing devices. Ted Speers, head of product architecture and planning for Microsemi’s SoC business unit, was appointed to the inaugural board of directors of the RISC-V Foundation in July 2016, and Ted Marena, director of SoC FPGA marketing, was recently elected as vice-chair of the RISC-V Marketing Committee.

Microsemi’s comprehensive software and IP core for RISC-V designs is available now.

Leave a Reply