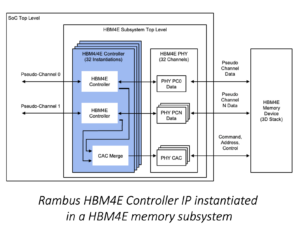

Rambus Inc. has released its HBM4E Controller IP designed for next-generation AI accelerators and high-performance computing. The controller supports data rates up to 16 Gbps per pin, providing 4.1 TB/s of throughput per memory device.

Rambus Inc. has released its HBM4E Controller IP designed for next-generation AI accelerators and high-performance computing. The controller supports data rates up to 16 Gbps per pin, providing 4.1 TB/s of throughput per memory device.

In an eight-device configuration, this architecture delivers over 32 TB/s of total memory bandwidth. The IP features low-latency operation and advanced reliability for intensive computational workloads. It integrates with third-party PHY solutions for 2.5D and 3D packages to support AI SoCs or custom base-die designs. Built on a foundation of over 100 previous HBM design wins, the controller aims to ensure first-time silicon success.

The HBM4E Controller IP is currently available for licensing and early access design engagement.

Leave a Reply