ASRock Industrial is thrilled to announce the launch of its latest innovation, the SBC-262M-WT 3.5” SBC Motherboard, a new benchmark in edge computing, powered by the advanced Intel Atom x7433RE Processor (Amston Lake). Designed with enhanced CPU and GPU performance, this motherboard ensures an optimal balance between performance, cost-efficiency, and versatility for various computing needs […]

Artificial intelligence

FPGA devices target software defined vehicle electronics

Efinix announced a line of FPGA solutions designed specifically for the automotive industry to drive forward the long-term design and development of the rapidly growing numbers of electronic applications in-and-outside vehicles. The line, now automotive qualified, and Efinix’s Efinity tool suite that has achieved ISO26262 certification extend the company’s capabilities for automotive manufacturers. The FPGA solutions for […]

JTAG probes support Renesas MPUs

The RZ/V2H is a single-chip MPU designed for next-generation robotics applications that require both vision AI and real-time control capabilities. With the integration of four Arm Cortex-A55 CPU cores, two Cortex-R8 cores, and one Cortex-M33 sub-core, the RZ/V2H can effectively manage both vision AI and real-time control tasks. SEGGER’s J-Link family of debug probes is […]

What are the challenges when testing chiplets?

Chiplet testing begins with performance simulations during the design process. Compared with monolithic devices, heterogeneous chiplets require more complex testing, including known good die (KGD) testing, final test, and system level test. Success also depends on the implementation of design for test (DfT) based on several IEEE standards. Chiplet designers need high-speed tools that can […]

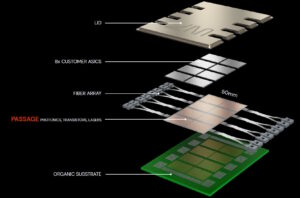

How can in-package optical interconnects enhance chiplet generative AI performance?

Generative artificial intelligence (AI) requires rapid and continuous movement of large amounts of data. In a growing number of instances, electrical input/output (I/O) connections between the ICs in chiplets are becoming a bottleneck to higher performance. Key electrical I/O performance barriers include power efficiency, bandwidth, and latency. This FAQ looks at the anticipated benefits of […]

Single-chip MPU bring vision AI to next-gen robotics

Renesas Electronics Corporation has expanded its popular RZ Family of microprocessors (MPUs) with a new device targeting high-performance robotics applications. Offering the highest levels of performance within the family, the RZ/V2H enables both vision AI and real-time control capabilities. The device comes with a new generation of Renesas proprietary AI accelerator, DRP (Dynamically Reconfigurable Processor)-AI3, […]

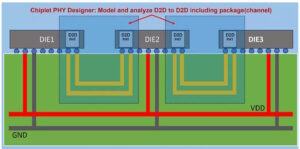

How do UCIe and BoW interconnects support generative AI on chiplets?

The bunch-of-wires (BoW) and Universal Chiplet Interconnect Express (UCIe) standards provide designers with tradeoffs in terms of throughput, interconnect density, delay, and bump pitch. This FAQ compares the performance of BoW and UCIe and looks at how optical interconnects may provide a path to even higher performance interconnects in chiplets. To realize optimal performance for […]

Advanced UWB IP supports FiRa 2.0 for high performance in dense, wireless areas

Ceva, Inc. announced the general release of its RivieraWaves ultra-wideband (UWB) IP for FiRa 2.0, the latest technical specification released by the FiRa industry consortium promoting standardization and compliance efforts for the widespread adoption of UWB-driven applications. Leveraging its unique low-power MAC-to-PHY solution, Ceva’s latest generation UWB IP includes a cutting-edge interference cancelation scheme to […]

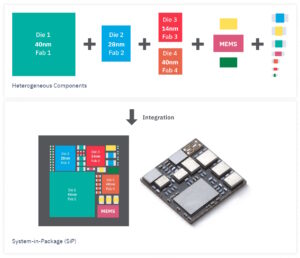

What is the heterogeneous integration roadmap, and how does it support generative AI?

The heterogeneous integration roadmap (HIR) is an ongoing initiative of the IEEE Electronics Packaging Society. It’s a living document that continues to evolve and expand in response to technological developments like the growth of generative artificial intelligence (AI) and quantum computing. This FAQ starts with a brief overview of heterogeneous integration, looks at the scope […]

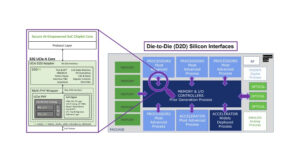

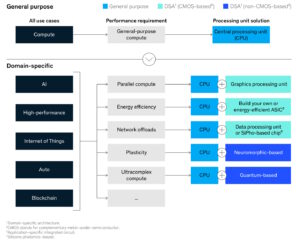

How does the open domain-specific architecture relate to chiplets and generative AI?

The Open Domain-Specific Architecture (ODSA) is a project within the Open Compute Project (OCP) community to establish open physical and logical die-to-die (D2D) interfaces for chiplets. The goal is to democratize the design and use of chiplets for domain-specific high-performance computing (HPC) applications like generative artificial intelligence (AI). Domain-specific architectures (DSAs) are an emerging approach […]