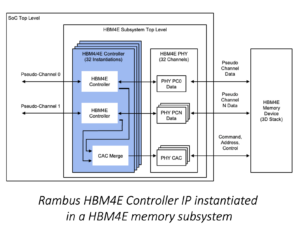

Rambus Inc. has released its HBM4E Controller IP designed for next-generation AI accelerators and high-performance computing. The controller supports data rates up to 16 Gbps per pin, providing 4.1 TB/s of throughput per memory device. In an eight-device configuration, this architecture delivers over 32 TB/s of total memory bandwidth. The IP features low-latency operation and […]

Artificial intelligence/ML

Radar, microphones, and MCUs address connected device security needs

Infineon takes the floor at Embedded World 2026 in Nuremberg, March 10 – 12 (Hall 4A, Booth 138) with live demonstrations spanning microcontrollers, sensors, automotive, and robotics. On the MCU side, engineers will see PSOC and AURIX devices running edge AI and robotics workloads with deterministic real-time control, alongside the TRAVEO SDV Zonal Demo, which […]

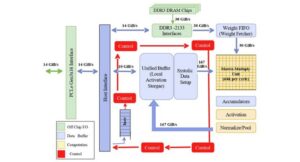

How to approach AI hardware design to address the memory wall?

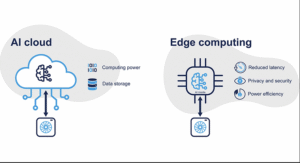

The transition from general-purpose computing to AI-specific hardware is driven by the specific computational and energy requirements of deep learning models. As these models scale to trillions of parameters, traditional architectures face the memory wall, where the energy required for data movement between memory and processing units significantly exceeds the energy consumed by the computation […]

AI-enabled workflows support automated V&V in toolchains

TASKING will be demonstrating its enhanced toolchain at Embedded World in Nuremberg. The end-to-end “compile, debug, test” toolschain integrates AI-driven workflows into embedded software development and verification, supporting functionally safe and secure real-time applications in automotive, aerospace and defense, industrial and robotics systems. Built on the Model Context Protocol, the toolchain enables large language models to […]

Neuromorphic processor reduces power in radar sensing systems

The jointly developed human-presence detection solution from Socionext and Innatera combines 60 GHz FMCW radar sensing with a neuromorphic Spiking Neural Processor to enable always-on detection at sub-milliwatt power levels. The system processes radar data directly at the edge to distinguish human from non-human motion, including stationary individuals, with reported accuracy above 99%, allowing connected […]

Edge AI applications include arc fault detection and condition monitoring

Microchip Technology has introduced full-stack edge AI solutions built around its microcontrollers and microprocessors to support real-time inferencing in industrial, automotive, data center and IoT applications. The platform integrates deployable pre-trained models, application code and development tools including MPLAB X IDE, MPLAB Harmony and the MPLAB ML Development Suite, enabling AI functions such as arc […]

Edge AI SoCs target robotics and automation under tight power budgets

Ambarella brings its edge AI SoC portfolio to Embedded World with live demos spanning robotics, industrial automation, automotive, and AIoT applications. The booth focuses on demonstrating AI performance per watt across Ambarella’s SoC lineup, with emphasis on running demanding workloads under tight power and latency constraints at the edge. Demos will cover both agentic AI, […]

COM Express 3.1 Type 6 Compact modules support -40 to +85 °C industrial temperature range

The conga-TCRP1 from congatec is a COM Express Type 6 Compact module built on AMD Ryzen™ AI Embedded P100 Series processors, combining up to 6 Zen5/Zen5c CPU cores, a Radeon™ RDNA™ 3.5 GPU and an XDNA2 NPU delivering up to 50 TOPS for edge AI workloads. The module supports up to 96 GB DDR5-5600 memory […]

What are the benefits of RISC-V in AI, ML, and embedded systems?

The open-source nature of RISC-V brings the benefits of a modular and royalty-free instruction set architecture (ISA) that eliminates licensing fees, can accelerate development, and fosters customization for diverse applications, including artificial intelligence (AI), machine learning (ML), the Internet of Things (IoT), and embedded systems. Automation levels are being increased in many types of applications, […]

How is physical artificial intelligence used to optimize data center efficiency?

Physical AI (PAI) in data center power systems uses machine learning for predictive maintenance, energy optimization, load balancing, and physical security. In essence, PAI is being used for data center optimization to support the demands of digital AI (DAI) applications like training large language models (LLMs), running inference for real-time applications, and supporting infrastructure like […]