A new successor to the Inter-Integrated Circuit (I2C or I2C) bus communication interface is under development, hosted by the Sensor Working Group at the MIPI Alliance. The Improved Inter-Integrated Circuit, I3C, (pronounced “Eye-three-See”) is backward compatible with I2C but will be better suited for handling an abundance of sensors. The I3C specification was released in early 2017 and promises a consistent way to interface to sensors which will reduce challenges with using sensors, since sensors today might use UART, SPI, or I2C. Integrating sensors to controllers would be easier with I3C as a standard. The Serial Peripheral Interface, or SPI, has a higher pin count than I2C or I3C and has been implemented in different ways. Thus, one can consider SPI to be less reliable by the hazard of having numerous improvements without a defined, global standard. I2C is in common use on mobile devices, but has no way for slave devices to initiate communication, has pull-up resistors that limit clock rate and decrease power efficiency. In 2013, the MIPI Alliance initiated work on a common sensor standard that would keep the best features of I2C and SPI but add features that would improve sensor integration. Besides providing one common standard to draw from, the overall benefits of I3C over I2C and SPI include lower implementation costs; I3C requires very little space inside sensors themselves. I3C also offers higher communication rates, and lower power consumption; all while maintaining backward compatibility with I2C. According to the MIPI Alliance, “The MIPI I3C standardized sensor interface is a game changer for integrated sensor systems. It has built a superset of features on top of the existing I²C (two-wire) interface with additional high data rate modes that can satisfy sensor use cases that currently require an SPI bus (four-wire).“

I2C was first created by Philips (now NXP) in 1982. For microcontrollers (MCUs), I2C has often been used to handle extra General Purpose I/O (GPIO) when all pins have been used on other things. Another option would be to multiplex your I/O, but that can take extra space on your board. It’s just easier to use any sensors that are I2C compatible on the I2C bus. However, I2C hasn’t had significant updates for over two decades now, and with so many sensors in use today for Internet of Things (IoT) applications, it’s understandable that I3C is on its way.

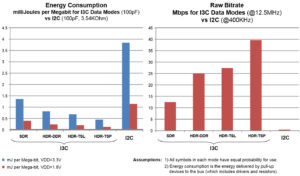

I3C is more power efficient than I2C, even while servicing I2C devices. I3C works well for anything that historically has used UART, SPI, or I2C and will be used to connect many components such as sensors, displays, always-on (low resolution) cameras, controllers, capacitive sensors, mobile applications, transducers, acoustics, and other peripherals. I3C will keep the 2-wire interface that’s present in I2C. I3C takes care of some historical pain points experienced with I2C having to do with in-band interrupts, dynamic addressing, handling multi-masters, and standardizing commands with common command codes. Issues with hot-joining, error detection, and error recovery experienced with I2C are also fixed in I3C. I3C also reduced energy consumption while providing higher data rates at 12.5 MHz versus the 400 kHz of I2C. All of these improvements will be experienced with I3C while maintaining full compatibility with legacy I2C devices.

New I3C features explained

In-band Interrupt

The 2-wire I3C interface uses a push-pull clock line (SCL) and an open drain data line (SDA). The SDA allows slaves to take control of the data line and initiate interrupts. (SPI and I2C can only provide slave interrupts by using a third, dedicated wire.) I3C slaves can request an interrupt when the bus is idle. I3C arbitrates conflicts from multiple slaves by allowing the lowest assigned address to win.

Hot-join

Hot-join describes an event where I3C slaves are allowed to join the I3C bus after the bus has been configured, enabling sensors to be shutdown until needed.

Increased Throughput

The master clock uses the SCL to clock the communication bus to 12.5 MHz. I3C supports multiple classes of devices: the I3C main master, an I3C secondary master, an I3C slave and an I2C slave. I3C has a standardized procedure for the master to dynamically assign 7-bit addresses to all I3C devices and support static device addresses of I2C devices on the same bus. I3C offers four data transfer modes that effectively provide data bit rates at 11.1, 20, 23.5, and 33.3 Mbps, including I3C bit rate error detection.

Dynamic Addressing

I2C uses static addressing. One of the problems here is that a vendor might use the same address as another vendor for a product that uses the I2C bus, causing issues during integration. I3C removes this problem by providing addressing for devices on the I3C bus.

More information, including a more detailed discussion of the advanced features of I3C can be found in the I3C specification on the MIPI Alliance website.

Great description