Rambus Inc. announced Compute Express Link (CXL) 2.0 and PCI Express (PCIe) 5.0 controllers now available with integrated Integrity and Data Encryption (IDE) modules. Delivering security at speed in CXL is critical to solving the bandwidth bottleneck in data center infrastructure. IDE monitors and protects against physical attacks on CXL and PCIe links. CXL requires extremely low latency to enable load-store memory architectures and cache-coherent links for its targeted use cases. This breakthrough controller with a zero-latency IDE, developed by the engineering team from newly acquired PLDA, delivers state-of-the-art security and performance at full 32 GT/s speed.

“Successful enablement of CXL use models in data-intensive applications, such as memory sharing between processors and attached AI accelerators, requires security at ultra-low latency,” said Sean Fan, chief operating officer at Rambus. “Delivering controllers with zero-latency security is a testament of our ability to accelerate the development of CXL solutions through the recent acquisition of PLDA, and showcases our unique position to provide integrated interface and security IP solutions.”

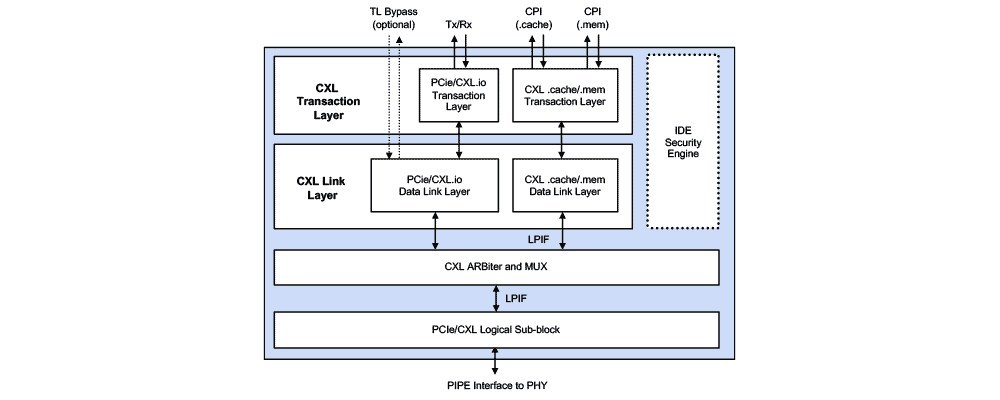

The built-in IDE modules, now available in Rambus CXL 2.0 and PCIe 5.0 controllers, employ a 256-bit AES-GCM (Advanced Encryption Standard, Galois/Counter Mode) symmetric-key cryptographic block cipher, helping chip designers and security architects to ensure confidentiality, integrity, and replay protection for traffic that travels over CXL and PCIe links. This secure functionality is especially imperative for data center computing applications including AI/ML and high-performance computing (HPC).

Key features include:

- IDE security with zero latency for CXL.mem and CXL.cache

- Robust protection from physical security attacks, minimizing the safety, financial, and brand reputation risks of a security breach

- IDE modules pre-integrated in Rambus CXL 2.0 and PCIe 5.0 controllers reduce implementation risks and speed time-to-market

- Complete CXL 2.0 and PCIe 5.0 interconnect subsystems when controllers are combined with Rambus CXL 2.0 and PCIe 5.0 PHYs

Leave a Reply