Synopsys announced the Synopsys PrimeECO design closure solution, the industry’s first signoff-driven solution that achieves signoff closure with zero iterations. Signoff closure has emerged as one of the top challenges in digital design implementation, consuming up to 50 percent of the design schedule, mainly driven by rapidly increasing signoff scenarios and physical complexity at advanced nodes. The PrimeECO solution uniquely combines the efficiency to manage unlimited signoff scenario views with the scalability of incrementally enabled integrated physical implementation and signoff capabilities, delivering a 10X productivity boost for system-on-chip (SoC) designers by eliminating costly iterations between implementation and signoff.

Synopsys announced the Synopsys PrimeECO design closure solution, the industry’s first signoff-driven solution that achieves signoff closure with zero iterations. Signoff closure has emerged as one of the top challenges in digital design implementation, consuming up to 50 percent of the design schedule, mainly driven by rapidly increasing signoff scenarios and physical complexity at advanced nodes. The PrimeECO solution uniquely combines the efficiency to manage unlimited signoff scenario views with the scalability of incrementally enabled integrated physical implementation and signoff capabilities, delivering a 10X productivity boost for system-on-chip (SoC) designers by eliminating costly iterations between implementation and signoff.

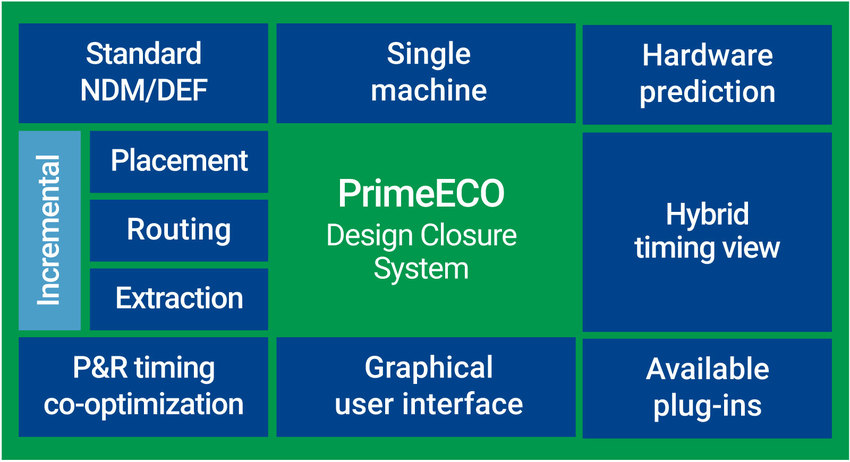

The PrimeECO design closure solution features an innovative machine-learning-driven Hybrid Timing View technology that addresses the increasing signoff scenarios by predicting optimal trade-offs between required compute resource and desired timing accuracy. The Hybrid Timing View deploys the PrimeTime® signoff engine for real-time updates on accuracy-critical scenarios, while ensuring complete visibility on coverage-critical scenarios through efficient static views. The efficiency of Hybrid Timing View enables thousands of timing scenarios to be loaded onto a single machine, eliminating the need for a large number of compute resources typically required for signoff coverage.

To further eliminate design iterations, PrimeECO is architected on the Fusion Design Platform™, the world’s first artificial intelligence (AI) enhanced, cloud-ready design platform with direct access to incrementally enabled placement, routing, extraction, physical verification, and signoff technologies from Synopsys’ market-leading portfolio of solutions, including IC Compiler™ II place-and route, Fusion Compiler™ RTL-to-GDSII, IC Validator physical verification, StarRC™ extraction, PrimeTime, PrimePower, and PrimeYield. Within this single-environment design closure cockpit, not only is every change fully implemented and validated, but it also creates new opportunities for placement, routing, and timing co-optimization to achieve power, performance, and area (PPA) results previously impossible in traditional design closure flows.

The exclusive PrimeECO solution is available to all designers innovating on the Fusion Design Platform, as well as industry-standard DEF databases. The intuitive cockpit also provides a unique graphical user interface to overlay Hybrid Timing View on design visualization for final touch-ups, including an open database interface available to custom scripts for user-driven optimization.

“Leading-edge customers continually face design-closure challenges due to growing design complexity and the fast-multiplying number of scenarios,” said Jacob Avidan, senior vice president of Engineering at Synopsys. “With the PrimeECO solution, we are introducing breakthrough technology that removes iterations during signoff closure by integrating key place-and-route technology into our golden signoff environment. That, coupled with the machine-learning-driven Hybrid Timing View for single machine efficiency, make this a game changer. We look forward to collaborating with our customers to address this critical need for signoff-driven design closure.”

Availability

PrimeECO will be available with the Synopsys 2019.12 release in December 2019.

Leave a Reply