The benefits of open source have been bestowed upon an Instruction Set Architecture (ISA) called RISC-V. One of the earliest, best-known examples of open source technology is Linux. For a widely accepted, official definition of open source, see The Open Source Initiative. Open source does not stop at Linux, however. One of the more recent open source initiatives is for the open source RISC-V, pronounced “risk five.” RISC-V is an extensible, base integer Reduced Instruction Set Computer (RISC) ISA and was begun at UC Berkeley as a 2010 “summer project” to create a simple ISA for classroom instruction that would have no legal entanglements as the intellectual property (IP) of another company. RISC-V took longer than expected to get out, and was officially launched as a royalty-free, open source project in 2015 by The RISC-V Foundation.

RISC-V was meant to be similar to other RISC ISAs, but also to be kept simple, yet also provide the ability for extensive customization and specialization. The base ISA can be expanded with standard optional extensions and opcodes for creating customized instructions. Thus, the RISC-V ISA extensions are divided into standard and non-standard extensions. The base integer instructions cannot be redefined, however.

One benefit of that simplicity is that RISC-V ISA can be used from small embedded processors up through high-performance supercomputers, spanning a broad range of applications. There are three different RISC-V instruction sets with addresses of 32-, 64-, and 128-bits in length. As mentioned above, open source also creates a standard whereby everyone knows what to expect and skill sets are portable across companies. RISC-V has the potential to save much time and effort in a very complicated area of engineering with a standard, portable ISA. As open source, anyone can take RISC-V ISA and change it or add proprietary portions. A standard, open ISA prevents wasted energy on “reinventing the wheel” in a very complex, advanced technology, thus benefitting many. An ISA does not directly affect performance or energy efficiency as much as how the ISA is used. As a necessary component of embedded processing that can add a good deal to the cost of an embedded system, RISC-V offers to save a considerable amount of time and money.

An added benefit is that RISC-V is now taught in a growing number of colleges, making graduates that much more valuable in the first year of employment. Research and education on ISAs have the potential to be more realistic, leveraging open software stacks and hardware. The introduction of the RISC-V User Manual states, “Our position is that the ISA is perhaps the most important interface in a computing system, and there is no reason that such an important interface should be proprietary. “

RISC-V currently has 4 base integer instruction sets that are each characterized by the width of their integer registers and the corresponding size of user address space. All use a two’ s complement to represent signed integers. The two primary base integer variants are RV32I and RV64I, which respectively support 32-bit and 64-bit user-level address spaces. RV32E is actually a subset variant of the RV32I base instruction set that was added to support small MCUs. A future 128-bit user address space characterizes the instruction base variant RV128I, which is accommodated by the RISC-V framework. Base ISAs and extensions are combined to indicate a custom ISA. E.g., RV32IMAC denotes 32-bit Integer + Atomic + Multiply + Compressed. RV64GC indicates that the ISA is 64-bit and supports integer, multiply, atomic, single- and double-precision floating-point, and compression to 16-bit instructions. RV64GCXext indicates IMAFDC and a non-standard extension, where “ext” is the name of the non-standard extension. Non-standard extensions (xext) are not described in the specification. See Table 1 for ISA name string options.

| Base | Version | ||

| RV32I | 32-bit Base integer ISA | 2.0 | Frozen |

| RV32E | Reduced version of RV32I for embedded systems | 1.9 | |

| RV64I | 64-bit Base integer ISA | 2.0 | Frozen |

| RV128I | 128-bit Base integer ISA | 1.7 | |

| Extensions | Standard extension for: | Version | |

| M | Integer multiplication and division | 2.0 | Frozen |

| A | Atomics | 2.0 | Frozen |

| F | Single-precision floating-point | 2.0 | Frozen |

| D | Double-precision floating-point | 2.0 | Frozen |

| Q | Quad-precision floating-point | 2.0 | Frozen |

| L | Decimal floating-point | 0.0 | |

| C | 16-bit Compressed instructions | 2.0 | Frozen |

| B | Bit manipulation | 0.0 | |

| J | Dynamically translated languages | 0.0 | |

| T | Transactional memory | 0.0 | |

| P | Packed-SIMD instructions | 0.1 | |

| V | Vector operations | 0.2 | |

| N | User-level interrupts | 1.1 | |

| Extensions | Stands for: | ||

| Xext | Non-standard extension “ext” | N/A | |

| G | General purpose, a moniker for the combined IMAFD | N/A |

Table 1: ISA name strings. Base ISAs and extensions can be combined to indicate a custom ISA.

Smaller code size can reduce cost in embedded systems. For instance, the amount of flash in a microcontroller often affects the price. Smaller code size can increase performance in cache-based cores as well. RV64 can also use the compressed instruction extension. Something reasonably unique with RISC-V is that you can have a 64-bit instruction in 16-bit architecture.

It would be challenging to cover RISC-V in detail without writing a book, so a small selection is included below.

The RISC-V Instruction Set Manual demonstrates the flexibility of the RISC-V ISA. The base RISC-V ISA is little-endian for accessing memory. Non-standard variants can be made to support big-endian or bi-endian memory systems, however. The load-store architectures only load and store instructions. Accessing memory and arithmetic instructions only operate on CPU registers. There are 32 integer registers in the RISC-V architecture with an additional, optional 32 floating point registers if FP is enabled. The width of the register is determined by the ISA. The RISC-V specification also describes an Application Binary Interface (ABI) which defines standard functions or registers, which is important for software interoperability.

RISC-V categorizes global and local interrupts. The two types of local interrupts are software and timer interrupts, with two local interrupts per hardware thread. Local interrupts are optional and would be used to connect peripheral devices (e.g., a UART interrupt). RISC-V defines global interrupts as an interrupt which can be routed to any hardware thread in a system.

RISC-V defines three levels of privileges called modes. Level 0 is for user or application layer privileges. Level 1 is for supervisor privileges. Level 2 is reserved and level 3 is machine level privileges. Machine mode is the only mode that is required and the highest privileged mode. This allows for a range of targeted implementations, including a least-complicated version where only machine mode is implemented. Machine and supervisor modes each have their own sets of control and status registers (CSRs).

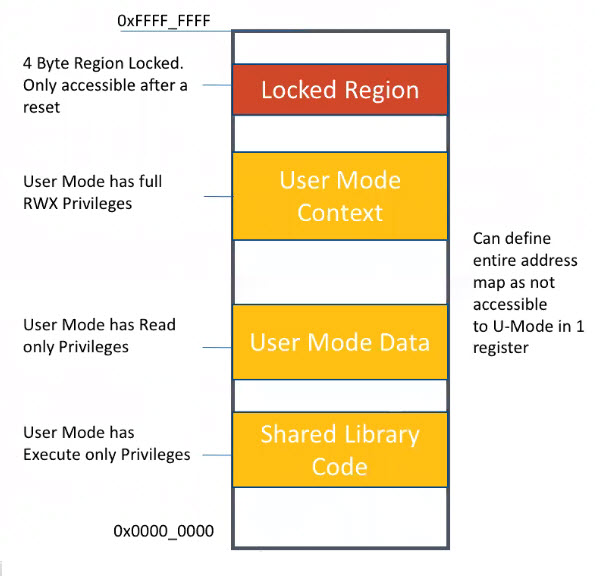

RISC-V has physical memory protection, which is used to enforce access restrictions on less privileged modes. With un-trusted user mode software, RISC-V can restrict which levels of memory that software has access to. The RISC-V physical memory protection scheme also has the ability to lock a region of memory. A locked area would enforce permissions on all accesses, including machine mode. This can be used, for example, to secure an area of memory after boot. The only way to unlock that region would be to reset the system. The physical memory protection scheme allows up to 16 protected regions with minimum region size of 4 bytes. RISC-V has support for virtual memory which allows for sophisticated memory management and operating system support.

RISC-V is intended to maintain constancy in the base and each standard extension over time. Changes can be made by layering new instructions as optional extensions. The base integer ISAs will continue to be fully supported as standalone ISAs, regardless of any subsequent extensions. The RISC-V ISA infrastructure includes documentation, ports to support a few operating systems, compiler toolchains, hardware implementations in FPGAs and ASICs, architecture test suites and simulators, community forums, and teaching materials. For more information, you can look at the RISC-V specifications, watch some RISC-V 101 webinars by SiFive, a company founded by the creators of RISC-V, or visit the RISC-V channel on YouTube.

Leave a Reply