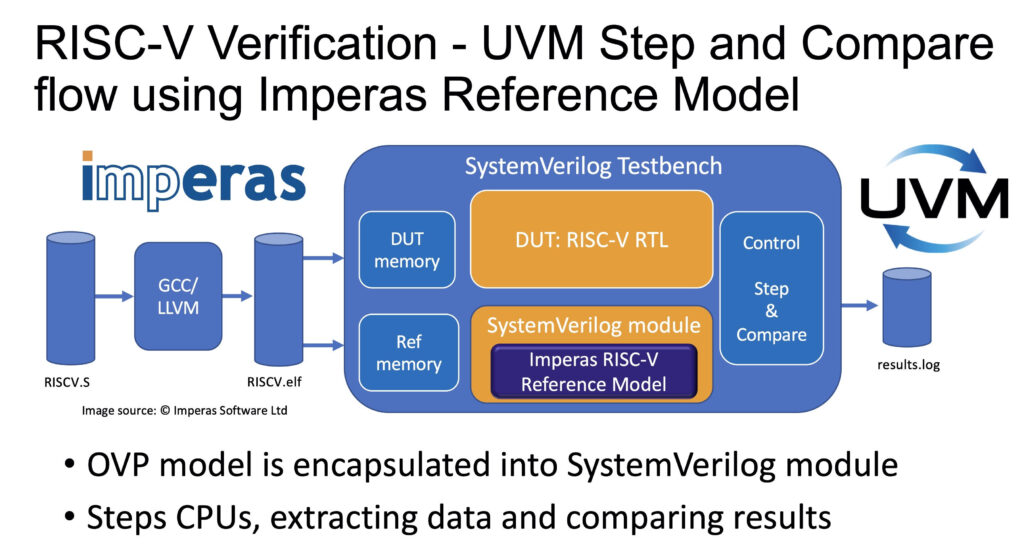

Imperas Software Ltd., announced the latest enhancements to its range of RISC-V reference models and solutions to support processor verification, with the leading commercial SystemVerilog hardware design verification environments provided by Cadence, Mentor, Synopsys, and also the Metrics cloud-based tools. Working together with lead customers, industry groups and associations, and the Google Instruction Stream Generator (ISG) developers, Imperas has enhanced the OVPsim reference models to support the comparison with directed tests, the RISC-V Foundation’s compliance tests, and tests created by the open source Google random ISG. The new approach to encapsulate the reference models within a SystemVerilog UVM (Universal Verification Methodology) test bench to allow a side-by-side comparison (step and compare verification) of RTL and reference model within the same environment for an interactive transaction-based analysis.

Imperas Software Ltd., announced the latest enhancements to its range of RISC-V reference models and solutions to support processor verification, with the leading commercial SystemVerilog hardware design verification environments provided by Cadence, Mentor, Synopsys, and also the Metrics cloud-based tools. Working together with lead customers, industry groups and associations, and the Google Instruction Stream Generator (ISG) developers, Imperas has enhanced the OVPsim reference models to support the comparison with directed tests, the RISC-V Foundation’s compliance tests, and tests created by the open source Google random ISG. The new approach to encapsulate the reference models within a SystemVerilog UVM (Universal Verification Methodology) test bench to allow a side-by-side comparison (step and compare verification) of RTL and reference model within the same environment for an interactive transaction-based analysis.

With this new release, hardware developers can for the first time use a golden reference model of a RISC-V processor alongside their RTL in their SystemVerilog UVM design verification (DV) environments.

The traditional view of the SoC design flow typically estimates that between 40 percent to 70 percent of the time and effort is directed at verification tasks. Based on the assumption of “known-good” semiconductor IP cores, the SoC verification is focused almost completely on the unique value-added features outside of the cores. Now with RISC-V, SoC developers can enjoy the additional design freedoms of an open ISA and explore options for customized, optimized instructions and extensions. In addition, the latest many-core SoCs can now utilize a broad range of individually optimized cores, each tailored to the rightsize requirements. Verification at the RISC-V core level is now an essential task for any SoC design with a custom processor, or custom instructions.

All processor developers need a full and detailed hardware verification environment although for many years the ISA and processor developers inside well-respected industry firms have built their own proprietary DV solutions and flows. It is only with RISCV that there is a need for the industry as a whole to have access to technologies that were traditionally proprietary and closed environments. This new Imperas release is the beginning of a hardware verification environment being made generally available to the wider community of designers, developers and DV engineers.

The simulation components of a complete DV test plan are based on 4 essential elements: the Device Under Test (DUT) RTL, the test framework, the quality reference model, and suitable tests to compare against. In addition to working with the Google ISG, Imperas has also contributed to the RISC-V Foundation working group on compliance, including the development of the latest RV32 test suites. For the RISC-V Vector extensions, Imperas has developed a new Vector compliance suite, and a directed test suite based on the latest draft specification. To support lead customers, these enhanced features and tests are being provided as an upgrade to the current Imperas commercial products and are already in active use.

The UVM encapsulation of the Imperas RISC-V reference model, testbench examples, application notes and documentation are available now for evaluation.

Leave a Reply