Get the basics on the SENT bus, which transmits sensor data to ECUs and other vehicle processors, one nibble at a time. How do you test the automotive SENT protocol? Test & Measurement Tips describes how to test the data bus. The Single Edge Nibble Transmission (SENT) protocol defines an approach to data communications in […]

Featured

Eclipse Temurin expands support to 54 version/platform combinations including RISC-V

The Eclipse Foundation, in collaboration with the Adoptium Working Group, has announced the latest release of Eclipse Temurin’s Java SE runtime. This release supports 54 version/platform combinations and five major OpenJDK versions, demonstrating Adoptium’s commitment to providing a diverse range of supported builds for Linux, Mac, Windows, and various architectures, including x64, ARM, and RISC-V. […]

How is Zephyr used for edge AI and sensors?

Zephyr is a scalable open-source real-time operating system (RTOS) hosted by the Internet of Things (IoT) and embedded technology section of the Linux Foundation. Its modular architecture makes it highly flexible and suitable for resource-constrained edge devices and sensors. This article reviews Zephyr’s structure and features, examines how Zephyr supports neural networks, and discusses how […]

How do AI and ML enhance SASE security?

Secure Access Service Edge (SASE) has emerged as a leading architecture for cloud deployments. Its primary function is to provide comprehensive cloud-based secure access while maintaining seamless access to data and applications for users of cloud computing services. This article compares SASE with a traditional network architecture and then looks at how artificial intelligence (AI) […]

How is HIL testing used for onboard EV chargers?

Hardware-in-the-loop (HIL) testing is a real-time simulation that enables designers to test embedded code for EV chargers without needing the actual system hardware. It speeds development efforts and reduces development costs. This article begins with an overview of HIL testing and onboard chargers (OBCs), looks at specific types of HIL testing applied to OBCs, and […]

How does a recurrent neural network (RNN) remember?

There are several types of neural networks (NNs). Recurrent NNs (RNNs) can “remember” data and use past information for inferences. This article compares recurrent NNs with feed-forward NNs (FFNNs) that can’t remember, then digs into the concept of backpropagation through time (BPTT) and closes by looking at long short-term memory (LSTM) RNNs. RNNs and FFNNs […]

EE Training Day: ADAS domain controllers and transition to central compute

ADAS domain controller trends bring more compute to the central ADAS ECU and reduce edge computing, leading to fully centralized compute modules in the next decade. This webinar covers the prevalent levels of autonomy today, how the new architectural trends align with increasing compute and autonomy features, and the impact of SW-defined vehicle trends in […]

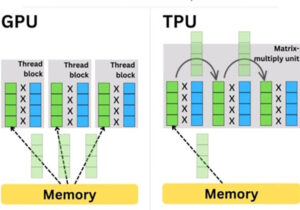

What’s the difference between GPUs and TPUs for AI processing?

Graphic processing units (GPUs) and tensor processing units (TPUs) are specialized ICs that support different types of artificial intelligence (AI) and machine learning (ML) algorithms. This article begins with a brief overview of tensors and where they fit into the mathematics of AI and ML; it then looks at the different structures of GPUs and […]

What are the programming essentials for LoRa nodes?

LoRa (long-range) technology ensures reliable long-range communication between a node and gateway, making it well-suited for a range of Internet-of-Things (IoT) applications. The purpose of building a LoRa node is to reduce costs while ensuring long-term, low-power use for devices. LoRa’s low power is affected by several features, covered below. Features Smart programming. The written […]

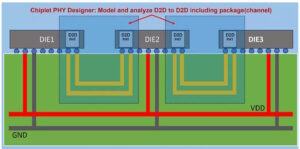

What are the challenges when testing chiplets?

Chiplet testing begins with performance simulations during the design process. Compared with monolithic devices, heterogeneous chiplets require more complex testing, including known good die (KGD) testing, final test, and system level test. Success also depends on the implementation of design for test (DfT) based on several IEEE standards. Chiplet designers need high-speed tools that can […]