MIPS announces its entrance to the RISC-V market, previewing the first products in its eVocore product lineup. The new eVocore P8700 and I8500 multiprocessor IP cores are the first MIPS products based on the RISC-V open instruction set architecture (ISA) standard.

eVocore products are designed to extend MIPS’ leadership in high-performance, real-time compute applications such as networking, data center, and automotive. According to Semico Research, the CAGR for SoCs shipping with RISC-V CPU cores between 2020 and 2027 is 73.6%, with the automotive segment projected to achieve a 69.9% CAGR during that time*.

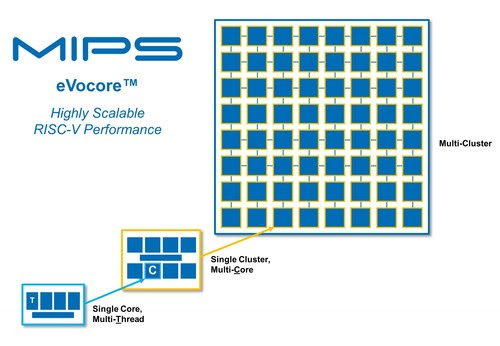

The new highly scalable and configurable RISC-V compatible eVocore IP cores are designed to provide performance leadership and a high level of scalability, enabling customers to blend coherent clusters of multi-threaded, multi-core CPUs in unique combinations to meet their exact power and performance requirements. The cores are designed to provide a flexible foundation for heterogeneous compute, supporting combinations of eVocore processors as well as other accelerators, with a Coherence Manager that maintains L2 cache and system-level coherency between all cores, main memory, and I/O devices.

Because the RISC-V ISA enables the addition of custom features in the form of user-defined instructions (UDIs), MIPS can uniquely deliver proven and powerful features which are required in many high-end applications, while also being fully compatible with off-the-shelf RISC-V development tools and software libraries.

Both of the new eVocore IP cores provide support for privileged hardware virtualization, user-defined custom extensions, multi-threading, hybrid debug, and functional safety. These features and the high level of scalability of the cores make them well suited for compute-intensive tasks across a broad range of markets and applications such as automotive (ADAS, AV, IVI), 5G and wireless networking, and data center and storage, and high-performance embedded applications.

eVocore P8700 – Superscalar Performance: This multiprocessing system combines a deep pipeline with multi-issue Out-of-Order (OOO) execution and multi-threading to deliver outstanding computational throughput. It has single-threaded performance greater than what is currently available in other RISC-V CPU IP offerings, and it can scale up to 64 clusters, 512 cores, and 1,024 harts/threads. The eVocore P8700 will be available in Q4 2022.

eVocore I8500 – Best-in-Class Performance Efficiency: This in-order multiprocessing system has best-in-class power efficiency for use in SoC applications. Each I8500 core combines multi-threading and an efficient triple-issue pipeline to deliver outstanding computational throughput.

Leave a Reply