While a new physical architecture can greatly simplify hardware deployment, an FPGA partitioning a requirement for multi-FPGA design. In October S2C already released an enhanced version of its Player Pro Compile software with a faster netlist partition engine, optimized black-box flow, and fully automated TCL scripting support. S2C will soon release RTL partitioning with hierarchical connectivity to address hyperscale designs that can easily span hundreds of FPGAs.

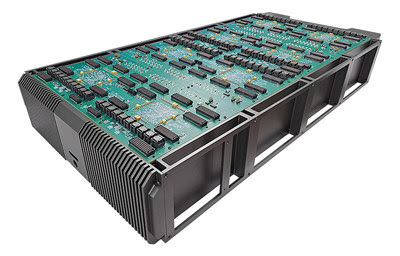

The first Logic Matrix series, LX1, and LX2 are based on Xilinx UltraScale VU440 and UltraScale+ VU19P respectively. LX1 offers up to an estimated 240M ASIC gates, 709Mb internal memory, 23K DSP slices, 19216 I/Os, and 384 GTH transceivers. LX2 offers up to an estimated 392M ASIC gates, 1.79Gb internal memory, 30.7K DSP slices, 12,672 I/Os, and 384 GTY transceivers.

Logic Matrix benefits from other S2C prototyping productivity tools. Player Pro Runtime software, included with the purchase of Prodigy prototyping systems, offers convenient features such as advanced clock management, integrated self-test, automatic board detection, I/O voltage programming, multiple FPGA downloads, remote system monitoring, and management. S2C’s Multi-Debug Module provides concurrent deep trace debugging and cross-triggers over multiple FPGAs. S2C’s ProtoBridge enables system-level co-modeling with a host PC and a PCIe/AXI connection to the device under test. S2C also offers a large library of off-the-shelf interface accessories as Prototype Ready IP to simplify access to real-world data and inter-system connectivity.

VU440 based Prodigy LX1 is available now for purchase. VU19P based LX2 and RTL partitioning are scheduled for Q2 2021 release.

Leave a Reply