IAR Systems presented a new version of its professional development tools for RISC-V. With the latest release, the complete development toolchain IAR Embedded Workbench for RISC-V adds support for the latest Andes RISC-V extension and devices, enabling maximized performance in RISC-V-based applications.

IAR Systems presented a new version of its professional development tools for RISC-V. With the latest release, the complete development toolchain IAR Embedded Workbench for RISC-V adds support for the latest Andes RISC-V extension and devices, enabling maximized performance in RISC-V-based applications.

Through its excellent optimization technology, IAR Embedded Workbench for RISC-V helps developers ensure the application fits the required needs and optimize the utilization of onboard memory. With the support of the AndeStar V5 RISC-V Performance Extension, developers can use IAR Embedded Workbench to create applications with increased performance and reduced code size. The toolchain supports all Andes 32-bit V5 RISC-V cores, including the N22, N25F, D25F, A25, A27, N45, D45, and A45. The RISC-V Packed SIMD/DSP extension specification (RVP draft) and the corresponding intrinsic functions, as well as Andes DSP libraries, are supported.

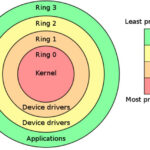

IAR Embedded Workbench for RISC-V is a complete C/C++ compiler and debugger toolchain with everything embedded developers need to be integrated into one single IDE. To ensure code quality, the toolchain includes C-STAT for static code analysis. C-STAT proves code alignment with industry standards like MISRA C:2012, MISRA C++:2008, and MISRA C:2004, and also detects defects, bugs, and security vulnerabilities as defined by CERT C and the Common Weakness Enumeration (CWE). For companies working with safety-critical applications, IAR Embedded Workbench for RISC-V is available in a functional safety edition certified by TÜV SÜD according to IEC 61508, ISO 26262, IEC 62304, EN 50128, EN 50657, IEC 60730, ISO 13849, IEC 62061, IEC 61511 and ISO 25119, delivering qualified tools, simplified validation, and guaranteed support through the product life cycle.

Leave a Reply