Xilinx, Inc. announced Vitis (pronounced Vī-tis), a unified software platform that enables a broad new range of developers – including software engineers and AI scientists – to take advantage of the power of hardware adaptability. The Vitis unified software platform automatically tailors the Xilinx hardware architecture to the software or algorithmic code without the need for hardware […]

synopsysinc

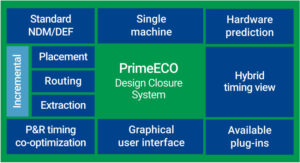

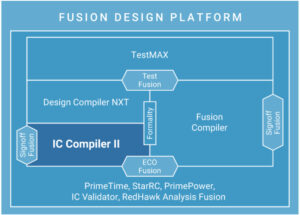

Digital SoC design software brings zero iterations between implementation and signoff

Synopsys announced the Synopsys PrimeECO design closure solution, the industry’s first signoff-driven solution that achieves signoff closure with zero iterations. Signoff closure has emerged as one of the top challenges in digital design implementation, consuming up to 50 percent of the design schedule, mainly driven by rapidly increasing signoff scenarios and physical complexity at advanced […]

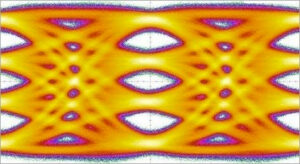

Ethernet PHY IP handles 800G networking apps

Synopsys announced its DesignWare 112G Ethernet PHY IP on TSMC’s N7 process supporting true long-reach channels for up to 800G networking applications. The DesignWare 112G PHY, based on Synopsys’ silicon-proven 56G Ethernet PHY available in multiple FinFET processes, delivers PAM-4 signaling for more than 35dB channel loss across optical, copper cables, and backplane interconnects. The […]

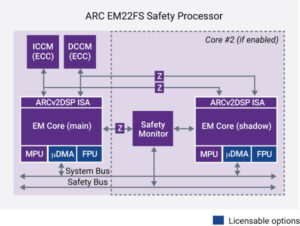

Processor IP supports ASIL B and ASIL D safety levels to simplify safety-critical automotive SoC development

Synopsys announced new functional safety (FS) derivatives of its popular DesignWare ARC processor IP to simplify and accelerate the development of automotive system-on-chips (SoCs). The safety-enhanced processor portfolio, which includes the Synopsys DesignWare ARC EM22FS, HS4xFS, and EV7xFS processors, covers a broad range of automotive use cases from ultra-low power control modules to artificial intelligence […]

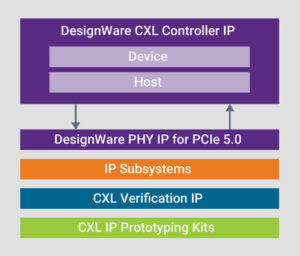

Chip design IP enables low-latency data comm among SoCs, general-purpose accelerators, memory expanders, smart I/O devices

Synopsys announced the availability of its complete DesignWare Compute Express Link (CXL) IP solution consisting of controller, PHY, and verification IP for AI, memory expansion, and high-end cloud computing system-on-chips (SoCs). The CXL protocol enables low-latency data communication between the SoC and general-purpose accelerators, memory expanders, and smart I/O devices requiring high-performance, heterogenous computing for […]

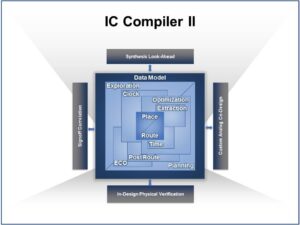

IC place-and-route software cuts power and chip area, speeds timing in new designs

Synopsys announced immediate availability of the latest release of its flagship IC Compiler II place-and-route system that includes several new innovative technologies to deliver superior quality-of-results (QoR) and fastest time-to-results (TTR) for the next wave of leading-edge designs across a wide range of vertical markets, including automotive, cloud computing, AI, networking and wireless applications. Continued […]

IC place-and-route package optimizes power use of chip designs

Synopsys announced immediate availability of the latest release of its flagship IC Compiler II place-and-route system that includes several new innovative technologies to deliver superior quality-of-results (QoR) and fastest time-to-results (TTR) for the next wave of leading-edge designs across a wide range of vertical markets, including automotive, cloud computing, AI, networking and wireless applications. Continued […]

Compute-intensive IP portfolio for 12-nm FinFET process targets AI, high-end smartphones

Synopsys announced its collaboration with GLOBALFOUNDRIES (GF) to develop a broad portfolio of DesignWare IP, including Multi-Protocol 25G, USB 3.0 and 2.0, PCI Express 2.0, DDR4, LPDDR4/4X, MIPI D-PHY, SD-eMMC, and Data Converters, for GF’s 12-nanometer (nm) Leading-Performance (12LP) FinFET process technology. Synopsys’ DesignWare IP on the GF 12LP process enables designers to implement the latest […]

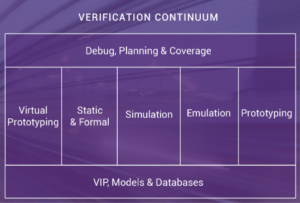

SoC verification software delivers 5X faster design load and tracing

Synopsys announced a new release of its Verification Continuum Platform with new native integrations across verification tools, enabling up to 5X higher verification performance. Verification Continuum is built from the industry’s fastest engines developed by Synopsys, including Virtualizer™ virtual prototyping, SpyGlass static and VC Formal® verification technologies, VCS simulation, ZeBu emulation, Synopsys HAPS prototyping, Verdi […]

Emulation-based power analyzer sized up billion-cycle software workloads

Synopsys announced its ZeBu Power Analyzer solution for software-driven system-on-chip (SoC) power analysis delivering results 1,000 times faster than traditional simulation-based methods. ZeBu Power Analyzer adds novel, multi-threaded power analysis engines to the industry-leading, high-performance ZeBu Server 4 emulation platform. It allows SoC design teams to systematically analyze power usage of their designs when executing […]