Feedback refers to a core concept in circuit design and control theory, used to stabilize amplifiers and control system behavior. This article outlines the fundamental architecture of feedback, classifies standard topologies, and examines a practical hardware implementation as a case study. What is the fundamental architecture of a feedback system? A feedback system consists of […]

FAQ

MCUs and MPUs, which does your project really need?

The basics of microcontroller units (MCUs) and microprocessor units (MPUs) haven’t changed too much. But application requirements have. What was once a simple automotive, industrial, or medical control system may now include edge AI processing, increasingly demanding security requirements, or complex 3D animated human machine interfaces (HMIs). That can change the game when choosing between […]

FAQ on Resistive Random Access Memory (RRAM)

There are many non-volatile memory technologies in use; RRAM is another option — maybe. Random access memory (RAM), sometimes called by a more descriptive name of read/write (R/W) memory, is critical to modern electronic systems. Small amounts are needed as a numeric scratchpad or to store data samples before processing; moderate amounts are needed to […]

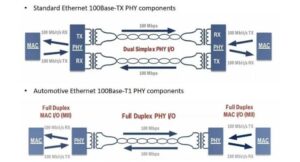

What is automotive Ethernet?

Automotive Ethernet is a physical layer standard that adapts standard Ethernet technology to the specific demands of the electric vehicle (EV) environment. This article examines how AE is evolving in-vehicle networking to meet the high-bandwidth, reliability, and architectural requirements of next-generation connected and autonomous vehicles. Networks, such as Controller Area Network (CAN) and Local Interconnect […]

Can chiplets save the semiconductor supply chain?

We’re making more semiconductors than ever before, and yet somehow, it’s still not enough. Demand is continuously increasing, spurred by the rise of AI in our everyday lives, but production still faces bottlenecks. The problem is more than just scale; it comes down to the structure of the manufacturing industry as a whole. As of […]

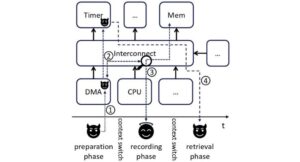

Beyond cryptography, what hardware-level vulnerabilities are a concern in SoCs?

Silicon security has traditionally focused on cryptography, including hardening crypto-accelerators and protecting key storage. In System-on-Chip (SoC) design, this approach is insufficient. An SoC integrates multiple components, such as cores, memory, and third-party IP blocks, onto a single die. This integration introduces hardware-level vulnerabilities that do not target the cryptographic algorithms themselves. Instead, these threats […]

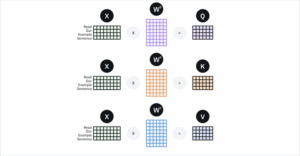

How is a transformer used in neural networks?

Transformers are a neural network (NN) architecture, or model, that excels at processing sequential data by weighing the importance of different parts of the input sequence. This allows them to capture long-range dependencies and context more effectively than previous architectures, leading to superior performance in natural language processing (NLP) tasks like translation and in computer […]

A practical guide to microcontroller structure and performance factors

Microcontroller units (MCUs) are single-chip computers optimized for performing embedded computing tasks like controlling a coffee machine or a medical device, an industrial robot, or an electric vehicle battery charger. They don’t require a complex operating system (OS) like those found on personal computers and servers. The central processing unit (CPU) is a key element […]

The intelligent Edge: powering next-gen Edge AI applications

Edge artificial intelligence (AI) technology is proving transformational for industrial enterprises as they shift focus toward the human- and planet-centric ideals of Industry 5.0. These solutions merge the power of edge computing with AI advancements to enhance efficiency, agility, and security through automation. They also reduce industrial reliance on centralized servers, helping to control both […]

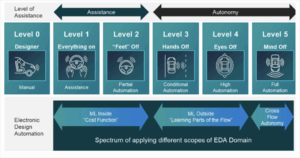

Reimagining EV design with AI-enhanced EDA tools

Artificial intelligence (AI)-driven chatbots, tools, and techniques are being deployed across various stages of electric vehicle (EV) design and simulation to support validation and manufacturing. AI can be used as an assistant to increase the effectiveness of conventional EDA tools. When combined with data-driven methods, it can also be used to create reduced-order models (ROMs) […]