by Matthew Ballance, Mentor, a Siemens Business In our previous article, The Nuts and Bolts of Verification: Recasting SystemVerilog for Portable Stimulus, we described how verification teams can jumpstart portable stimulus test description creation using existing SystemVerilog constructs and principles. Now, switching from analogy to idiom, we’ll dive into the “nuts and bolts” of how […]

siemens

The nuts and bolts of verification: Recasting SystemVerilog for Portable Stimulus

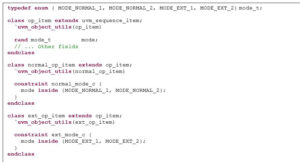

by Matthew Ballance, Mentor, a Siemens Business Nuts and bolts. So prosaic, yet so fundamental and essential. They can be reused, mixed-and-matched in endless ways. All those old jars and tins full of leftover nuts, bolts, and screws have saved many trips to the hardware store. Yet, if not for standardized gauge, thread count, and […]

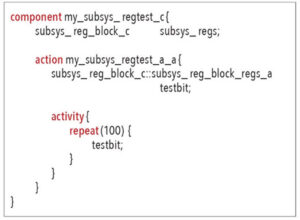

How to create and run reusable register-test models

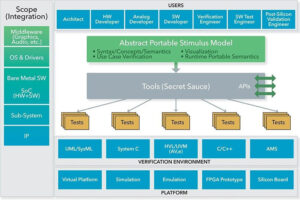

by Matthew Ballance, Mentor, a Siemens Business Register tests are a very useful smoke test at all design levels — from IP to subsystem to SoC. While the built-in register-test sequences in the UVM library are useful at the IP level, capturing register-test intent in a PSS model makes register-test functionality portable from the IP […]

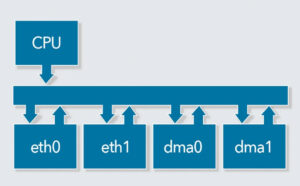

Retargeting existing tests in an integrated SoC verification flow

by Matthew Ballance, Mentor, a Siemens Business The raison d’etre for portable stimulus is reuse. The Accellera Portable Stimulus Standard (PSS) promotes test intent reuse throughout the verification process and across the multiple engines on which those verification runs are performed. Test intent captured as portable stimulus models enables test reuse from the IP to […]

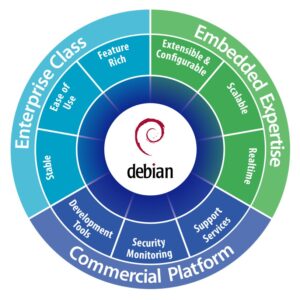

Enterprise-class embedded Linux covers multiple processor architectures

With the growth of internet of things (IoT) and other smart devices, it is becoming increasingly complex and expensive for manufacturers to develop embedded distributions and applications for these devices based on the Linux operating system. Siemens PLM Software today announced a new enterprise Mentor Embedded Linux (MEL) solution that provides electronics manufacturers secure, scalable and configurable distributions […]

Embedded Computing LEAP Awards winners announced at gala dinner

At the LEAP Awards dinner gala in Costa Mesa, Calif., the following companies were awarded trophies in the category of Embedded Computing. This year’s inaugural LEAP Awards competition honored ground-breaking new products that set a new standard for innovation. Judges rated candidates on categories that included societal impact, industry impact, technical sophistication, creativity, and value […]

Finalists announced for inaugural Embedded Computing category in LEAP Awards

Three finalists were announced for the inaugural LEAP Awards’ Embedded Computing Category, comprising innovative products and technologies. The competition was scored by a panel of independent technical/engineering-oriented judges. Responsible for the Embedded Computing category were these four judges: Plamen Doynov Research Professor University of Missouri-Kansas City Plamen Doynov became a research professor in physics last […]

IC design software includes automotive-grade automatic test pattern generation technology

Mentor, a Siemens business, today announced the availability of automotive-grade automatic test pattern generation (ATPG) technology for its Tessent TestKompress software. The new technology includes a suite of fault models and test pattern generation applications that target defects in ICs at the transistor and interconnect levels – in the process helping customers capture defects that […]

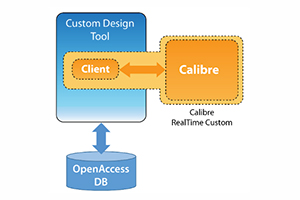

EDA, Spice software supports TSMC 7-nm FinFET Plus, 5-nm FinFET processes

Mentor, a Siemens business, today announced certification for TSMC’s 7nm FinFET Plus and the latest version of 5nm FinFET processes for its Mentor Calibre nmPlatform and Analog FastSPICE (AFS) Platforms. In addition, Mentor continues to expand features of both the Xpedition Package Designer and Xpedition Substrate Integrator products supporting TSMC’s advanced packaging offerings. Mentor Calibre nmPlatform for TSMC 5nm and 7nm FinFET Plus […]

Design tool generates photonic layouts for fabrication

Mentor, a Siemens business, today announced LightSuite Photonic Compiler – the industry’s first integrated photonic automated layout system. This new tool enables companies designing integrated photonic layouts to describe designs in the Python language, from which the tool then automatically generates designs ready for fabrication. The resulting design is “Correct by Calibre” – with the […]