Mentor announced that TSMC has certified multiple Mentor product lines and tools for the foundry’s recently announced 3nm (N3) process technology. The Mentor offerings now certified for TSMC’s N3 process include the Analog FastSPICE Platform, which provides leading-edge circuit verification for nanometer analog, radio frequency (RF), mixed-signal, memory and custom digital circuits. Mentor has also […]

mentor

SoC design software helps ID systemic errors early in development

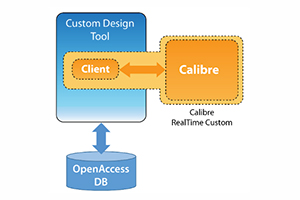

To help integrated circuit (IC) designers achieve design closure faster, Mentor, a Siemens business, today announced the extension of their powerful Calibre Recon technology to the Calibre nmLVS circuit verification platform. Introduced last year as an extension to Mentor’s Calibre nmDRC suite, the Calibre Recon technology is designed to enable customers to rapidly, automatically and […]

IC physical, circuit verification software certified for high-performance process technologies

Mentor, a Siemens business, announced that it has achieved certification for a broad array of Mentor integrated circuit (IC) design tools for TSMC’s industry-leading N5 and N6 process technologies. In addition, Mentor’s collaboration with TSMC has extended to advanced packaging technology, further leveraging Mentor’s Calibre platform 3DSTACK packaging technology to support TSMC’s advanced packaging platforms. […]

A new technique to maximize scan diagnosis throughput

by Jayant D’Souza, product manager Tessent group at Mentor, a Siemens Business Charged with the task of improving yield, product engineers need to find the location of defects in manufactured ICs quickly and efficiently. Typically, they use failing test cycles to perform scan diagnosis, which is then analyzed to reveal the location and root cause […]

IC design software handles 22-nm ultra-low-power process technology

Mentor, a Siemens business, announced that multiple Mentor product lines are now certified for United Microelectronic Corporation’s (UMC’s) 22uLP (ultra Low Power) process technology, including Mentor’s Calibre platform, Analog FastSPICE platform, and Nitro-SoC digital design platform. UMC’s 22nm process features 10 percent area reduction, improved power-to-performance ratio and enhanced RF capabilities compared to the company’s […]

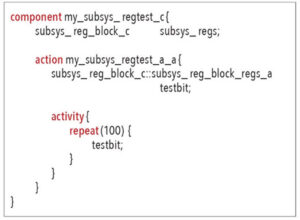

How to create and run reusable register-test models

by Matthew Ballance, Mentor, a Siemens Business Register tests are a very useful smoke test at all design levels — from IP to subsystem to SoC. While the built-in register-test sequences in the UVM library are useful at the IP level, capturing register-test intent in a PSS model makes register-test functionality portable from the IP […]

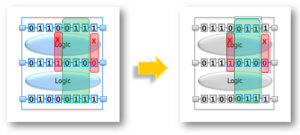

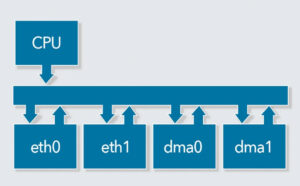

Retargeting existing tests in an integrated SoC verification flow

by Matthew Ballance, Mentor, a Siemens Business The raison d’etre for portable stimulus is reuse. The Accellera Portable Stimulus Standard (PSS) promotes test intent reuse throughout the verification process and across the multiple engines on which those verification runs are performed. Test intent captured as portable stimulus models enables test reuse from the IP to […]

Finalists announced for inaugural Embedded Computing category in LEAP Awards

Three finalists were announced for the inaugural LEAP Awards’ Embedded Computing Category, comprising innovative products and technologies. The competition was scored by a panel of independent technical/engineering-oriented judges. Responsible for the Embedded Computing category were these four judges: Plamen Doynov Research Professor University of Missouri-Kansas City Plamen Doynov became a research professor in physics last […]

EDA, Spice software supports TSMC 7-nm FinFET Plus, 5-nm FinFET processes

Mentor, a Siemens business, today announced certification for TSMC’s 7nm FinFET Plus and the latest version of 5nm FinFET processes for its Mentor Calibre nmPlatform and Analog FastSPICE (AFS) Platforms. In addition, Mentor continues to expand features of both the Xpedition Package Designer and Xpedition Substrate Integrator products supporting TSMC’s advanced packaging offerings. Mentor Calibre nmPlatform for TSMC 5nm and 7nm FinFET Plus […]

Design tool generates photonic layouts for fabrication

Mentor, a Siemens business, today announced LightSuite Photonic Compiler – the industry’s first integrated photonic automated layout system. This new tool enables companies designing integrated photonic layouts to describe designs in the Python language, from which the tool then automatically generates designs ready for fabrication. The resulting design is “Correct by Calibre” – with the […]