Imagination Technologies announces the Imagination DXTP GPU IP, designed to accelerate graphics and compute workloads on smartphones and other power-constrained devices. The DXTP delivers 20% improved power efficiency (FPS/W) on graphics workloads compared to its DXT equivalent through micro-architectural improvements. The DXTP provides 64 GPixel/s, 2 TFLOPS FP32, and 8 TOPS INT8 in a compute […]

Artificial intelligence/ML

Display combines Pi compute with Clea OS

SECO S.p.A. and Raspberry Pi Ltd announce the presentation of the cutting-edge Human-Machine Interface (HMI) solution, the SECO Pi Vision 10.1 CM5 powered by Raspberry Pi Compute Module 5, at Embedded World 2025, the premier trade show for embedded technologies taking place from March 11-13 in Nuremberg, Germany. This new integrated solution underscores the companies’ shared […]

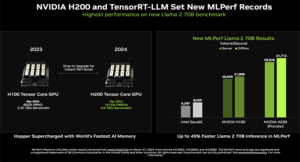

What are the different MLPerf benchmarks from MLCommons?

Formulated and managed by MLCommons, MLPerf benchmarks measure key operational parameters of artificial intelligence (AI) accelerators across multiple industries. These standardized metrics help semiconductor companies optimize performance and support the development of efficient AI chip designs. This article discusses MLPerf’s crucial role in facilitating comprehensive benchmark testing for tiny and edge computing systems while scaling […]

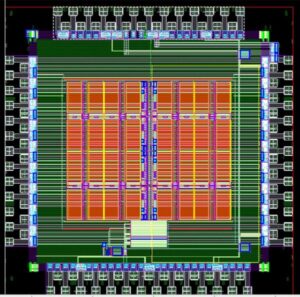

Memory stack design reaches 4 TB/s bandwidth with eight dies

Numem will be at the upcoming Chiplet Summit to showcase its high-performance solutions. By accelerating the delivery of data via new memory subsystem designs, Numem solutions are re-architecting the hierarchy of AI memory tiers to eliminate the bottlenecks that negatively impact power and performance. The rapid growth of AI workloads and AI Processor/GPUs are exacerbating the memory bottleneck […]

Chip design framework shows 2-3x efficiency for AI processing

Arm has released the first public specification of its Chiplet System Architecture (CSA), a framework for standardizing chipset connectivity and system partitioning. The specification is now supported by more than 60 technology companies, including ADTechnology, Alphawave Semi, AMI, Cadence, Jaguar Micro, Kalray, Rebellions, Siemens, and Synopsys. The CSA framework enables designers to create reusable chipsets […]

Accelerating high-performance AI workloads with photonic chips

Artificial intelligence (AI) and machine learning (ML) continue to push the limits of conventional semiconductor architectures. To increase speeds, lower latency, and optimize power consumption for high-performance workloads, semiconductor companies and research institutions are developing advanced photonic chips that operate on the principles of light rather than electrical currents. This article discusses the limitations of […]

How to minimize design cycles for AI accelerators with advanced DFT and silicon bring-up

Design for testability (DFT) embeds testable features into an integrated circuit (IC) during design, while silicon bring-up initiates chip evaluation and debugging. Streamlining these sequential processes minimizes design cycles and shortens time-to-market (TTM) for advanced artificial intelligence (AI) accelerators. This article explores the complexities of AI chip design and outlines strategies for optimizing DFT and […]

Industrial motherboards support DDR5, PCIe Gen 5, and USB4

ASRock Industrial unveils its newest range of industrial motherboards, powered by Intel Core Ultra 200S Processors (Arrow Lake-S) with Intel 800 series chipsets. Featuring an advanced hybrid architecture with up to 24 cores and an upgraded NPU, these motherboards empower exceptional edge performance, energy efficiency, and enhanced AI acceleration for complex AI-driven workloads. The new range […]

Edge GenAI SoC supports 12 simultaneous 1080p30 video streams

Ambarella, Inc. announced during CES the N1-655 edge GenAI system-on-chip (SoC), which provides on-chip decode of 12x simultaneous 1080p30 video streams, while concurrently processing that video and running a hybrid of multiple, multimodal vision-language models (VLMs) and traditional CNNs. This SoC’s high AI processing performance supports most of the popular multimodal VLMs and large-language models […]

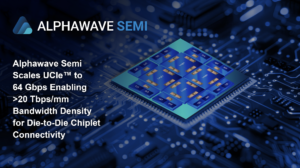

Die-to-die interconnect achieves 64 Gbps data rates with enhanced protocol support

Alphawave Semi introduces the industry’s first 64 Gbps Universal Chiplet Interconnect Express (UCIe) Die-to-Die (D2D) IP Subsystem to deliver unprecedented chipset interconnect data rates, setting a new standard for ultra-high-performance D2D connectivity solutions in the industry. The third generation, 64 Gbps IP Subsystem builds on the successes of the most recent Gen2 36 Gbps IP […]