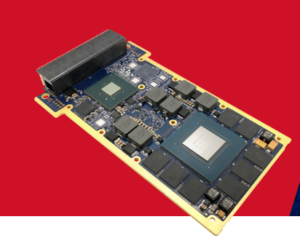

Aetina has launched new embedded MXM GPU modules powered by the NVIDIA RTX family, including RTX A1000, RTX A2000, and RTX A4500. These NVIDIA Ampere architecture-based MXM GPU modules, providing superb performance and power efficiency, are suitable for various types of computer vision applications across different industries such as commercial gaming, aerospace, healthcare, and manufacturing. […]

Artificial intelligence

Omnivision wins coveted 2022 LEAP Award

Omnivision took home the bronze medal in the recently completed 2022 Leap Awards for product innovation. The LEAP Awards celebrates the most innovative and forward-thinking products serving the design engineering space. Omnivision won in the Embedded Computing category, which includes microcontrollers (MCUs) or microprocessors (MPUs) or other custom-designed chips, and supporting software in ROM (Read […]

3U OpenVPX GPGPU processor module combines NVIDIA Ampere GPU, Gen4 PCIe switch

Curtiss-Wright’s Defense Solutions division introduced the VPX3-4936, its first 3U OpenVPX GPGPU processor module to feature the combination of NVIDIA’s Ampere GPU and a configurable Gen4 PCIe Switch. The NVIDIA Ampere architecture offers a significant boost in performance and efficiency over the previous NVIDIA Turing generation, including more flexible concurrent execution of floating point and integer […]

Rugged SFF embedded computer targets unmanned, autonomous missions

Systel introduced Kite-Strike II at the 2022 AUSA Annual Meeting and Exposition. Kite-Strike II is a next-generation, fully rugged small form factor (SFF) embedded computing solution, providing a massive leap forward in edge-deployed AI compute technology and capabilities for unmanned and autonomous missions. Systel introduces Kite-Strike II, the world’s first fully rugged NVIDIA Jetson AGX Orin compute […]

Distributed, ruggedized computing modules target defense apps

General Micro Systems announced the launch of its X9 Spider family of distributed, ruggedized computing modules to support the demanding needs of next-generation warfare. Through its innovative inter-locking mechanical design, MOSA Thunderbolt interfaces, OpenVPX cross-platform compatibility, and patented LightBolt connectors, the X9 Spider family empowers designers to decentralize, distribute, and rapidly upgrade computing, networking, storage, artificial […]

3U/6U OpenVPX computer boards, peripherals, ATR-style chassis target defense apps

General Micro Systems introduced a new product family of 3U and 6U OpenVPX computer boards, peripherals, and ATR-style chassis for use in U.S. Army ground, air, communications, and weapons systems. The “X9 Venom” family of 21 products will be available by early 2023, starting first with the 3U and 6U single-board computers (SBCs) based upon […]

ECO software speeds chip design tasks

To boost productivity and enhance the power, performance, and area (PPA) of advanced electronic designs, Synopsys, Inc. announced the breakthrough golden signoff ECO solution that addresses lengthy engineering design closure times. The Synopsys PrimeClosure solution combines Synopsys’ leading engineering change order (ECO) signoff solutions, Synopsys PrimeECO and Synopsys Tweaker ECO, with breakthrough innovations, delivering the fastest ECO […]

Quad-core ARM processor boosts space, edge, AI computing apps

Teledyne e2v announces the delivery of qualified flight models (FMs) of its advanced, space-qualified, quad-core Cortex-A72 edge processing platform – the LS1046-space. Targeting compute-intensive space applications, including high-throughput satellites, data compression, as well as artificial intelligence, and imaging, this processor outperforms existing alternatives by a factor of 30x. This timely addition to Teledyne e2v’s portfolio […]

MPUs feature built-in vision AI accelerator for image recognition, multi-camera image support

Renesas Electronics Corporation has expanded its AI-capable RZ/V Series of microprocessors (MPUs), with a new device that enables AI processing of image data from multiple cameras, offering a new level of highly accurate image recognition for vision AI applications. Equipped with two 64-bit Arm Cortex-A53 cores, the new device is capable of delivering high computing […]

Vision IC supports dual-channel 4K ISP, enhanced AI processing, depth sensing

Inuitive Ltd. announced the launch of its new NU4100, an expansion of its Vision and AI IC portfolio. Based on Inuitive’s unique architecture and advanced 12nm process technology, the new NU4100 IC supports integrated dual-channel 4K ISP, enhanced AI processing, and depth sensing in a single-chip, low-power design, setting the new industry standard for Edge-AI […]